Visible to Intel only — GUID: azl1475769383630

Ixiasoft

1. DisplayPort Intel® FPGA IP Design Example Quick Start Guide

2. DisplayPort Design Examples

3. HDCP Over DisplayPort Design Example for Intel® Arria® 10 Devices

4. DisplayPort Intel® Arria® 10 FPGA IP Design Example User Guide Archives

5. Revision History for DisplayPort Intel® Arria® 10 FPGA IP Design Example User Guide

2.1. Intel® Arria® 10 DisplayPort SST Parallel Loopback Design Features

2.2. Intel® Arria® 10 DisplayPort MST Parallel Loopback Design Features

2.3. Enabling Adaptive Sync Support

2.4. Intel® Arria® 10 DisplayPort SST TX-only or RX-only Design Features

2.5. Design Components

2.6. Clocking Scheme

2.7. Interface Signals and Parameters

2.8. Hardware Setup

2.9. Simulation Testbench

2.10. DisplayPort Transceiver Reconfiguration Flow

2.11. Transceiver Lane Configurations

Visible to Intel only — GUID: azl1475769383630

Ixiasoft

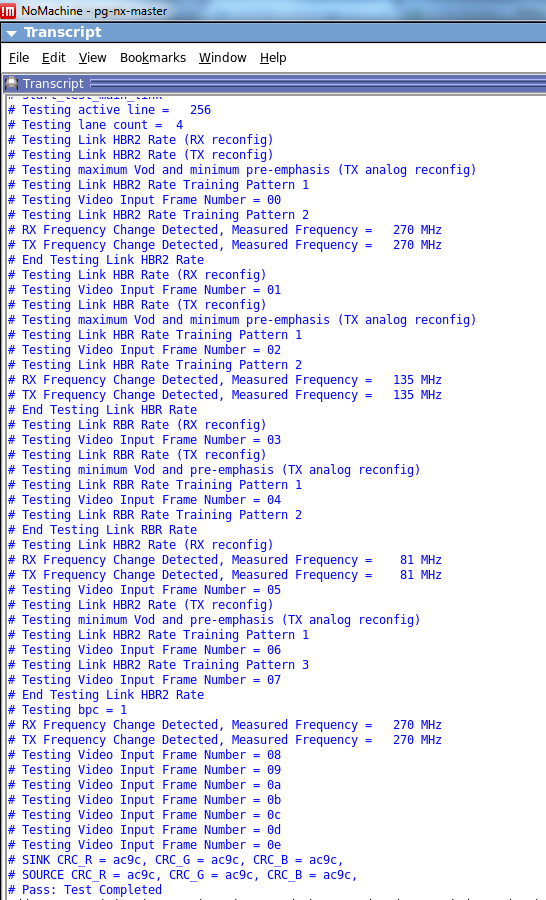

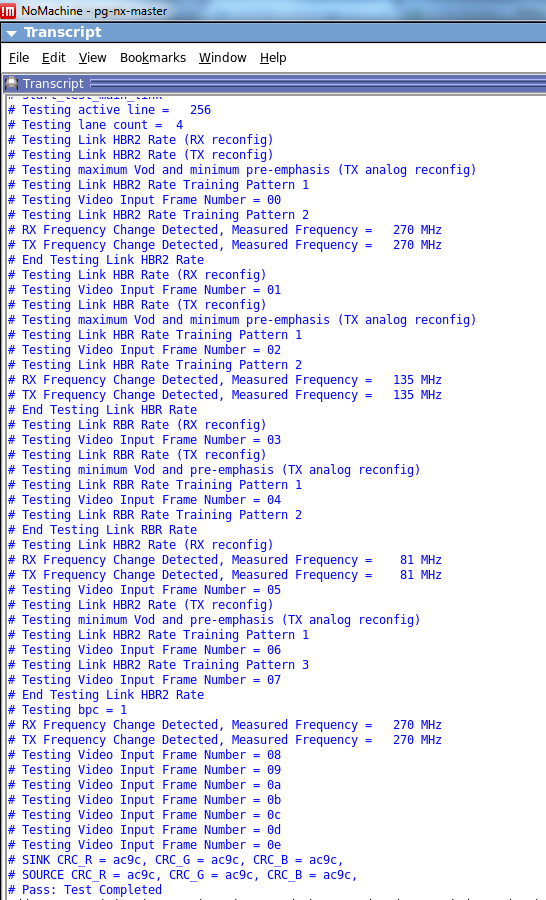

2.9. Simulation Testbench

The simulation testbench simulates the DisplayPort TX serial loopback to RX.

Figure 12. DisplayPort Intel® FPGA IP Simplex Mode Simulation Testbench Block Diagram

| Component | Description |

|---|---|

| Video Pattern Generator | This generator produces color bar patterns that you can configure. You can parameterize the video format timing. |

| Testbench Control | This block controls the test sequence of the simulation and generates the necessary stimulus signals to the TX core. The testbench control block also reads the CRC value from both source and sink to make comparisons. |

| RX Link Speed Clock Frequency Checker | This checker verifies if the RX transceiver recovered clock frequency matches the desired data rate. |

| TX Link Speed Clock Frequency Checker | This checker verifies if the TX transceiver recovered clock frequency matches the desired data rate. |

The simulation testbench does the following verifications:

| Test Criteria | Verification |

|---|---|

|

Integrates Frequency Checker to measure the Link Speed clock's frequency output from the TX and RX transceiver. |

|

|

A successful simulation ends with the following message:

| Simulator | Supported Platform | Supported Language |

|---|---|---|

| Riviera-PRO* | Windows/Linux | VHDL and Verilog HDL |

| ModelSim* | Windows/Linux | VHDL and Verilog HDL |

| Xcelium* Parallel | Linux | Verilog HDL |

| VCS* / VCS* MX | Linux | VHDL and Verilog HDL |