Visible to Intel only — GUID: mba1628537157921

Ixiasoft

Visible to Intel only — GUID: mba1628537157921

Ixiasoft

1.4. Plane Capacitance

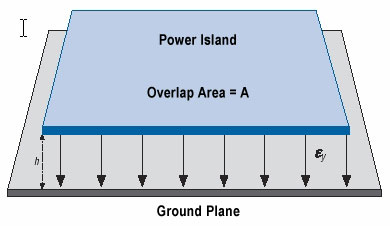

For high frequencies, decoupling using discrete capacitors is less effective. Use power plane capacitance for decoupling noise at these frequencies. You can understand the concept of plane capacitance by studying the classic parallel plate capacitor, as shown in Figure 1.

An electric field is created when there is a power plane next to a ground plane. The upper area in Figure 1 shows the power island or plane, the lower area shows the ground plane, and the arrows represent the electric field lines. This electric field gives rise to a capacitance, the magnitude of which is shown by the following equation:

C=(εοεrA)/h

Where

- εο = permittivity of free space

- εr = relative permittivity of the dielectric used

- A = area of overlap

- h = separation of the planes.

If there are ground planes on both sides of the power island, then the capacitance needs to be calculated for each side and added to determine the total capacitance.

Plane capacitance is the primary way of decoupling at high frequencies, so it must be an integral part of any high-speed design. At high frequencies, the discrete capacitors are not very effective.

As an example, consider the following.

Example: Determine the parallel plate capacitance for 1 square inch of area overlap in an FR-4 dielectric (εr = 4.5) and a separation of 4 mils.

Solution:

Applying these numbers to the capacitance equation above yields C = 253 pF. Therefore, there is about 253 pF per square inch of area overlap on a typical FR-4 board with 4 mils of separation. The value scales inverse linearly with separation and linearly with area.