Visible to Intel only — GUID: dlt1628537169299

Ixiasoft

Visible to Intel only — GUID: dlt1628537169299

Ixiasoft

1.5.5. Inter-Plane Capacitance

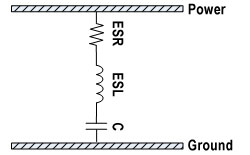

As a first-order analysis, the PCB power-ground plane pair can simply be modeled as a series connected resistor, inductor, and, capacitor as shown in Figure 6. Note that this simple model ignores the frequency dependent effects such as skin effect and dielectric absorption.

The first-order equations for the ESL in Figure 6 is shown below:

- ESL = (μ0•h•l)/w

Where,

- μ0 = magnetic permeability of free space (32 pH/mil)

- h = distance between the power and ground planes in mils

- l = length of the power plane in inches

- w = width of the power plane in inches

You can interpret the ESL of the power-ground plane sandwich as the spreading inductance that the decoupling capacitor sees as it is supplying current to the BGA device. Therefore, from the ESL equation above, the spreading inductance can be reduced by placing the decoupling capacitors as close as possible to the target BGA device (minimizing the distance l from the cap to the BGA device). Additionally, using a thin dielectric material (minimizing h) and wide plane pairs (maximize w) for the power-ground plane sandwich helps reduce the effective spreading inductance seen by the decoupling capacitor.