Visible to Intel only — GUID: nik1412634856149

Ixiasoft

1.4.1. Creating the Qsys System

1.4.2. Creating the Transceiver Native PHY IP

1.4.3. Creating the Reconfiguration Controller

1.4.4. Creating the CMU PLL Using an Arria V Transceiver PLL

1.4.5. Creating a Fractional PLL (fPLL) using Altera PLL

1.4.6. Creating the Transceiver PHY Reset Controller

1.4.7. Creating a ROM that Contains the MIF for Reconfiguration

1.4.8. Compiling the Design Example

1.4.9. Creating In-System Sources and Probes (ISSP)

1.4.10. Performing Reconfiguration with the System Console Tool

Visible to Intel only — GUID: nik1412634856149

Ixiasoft

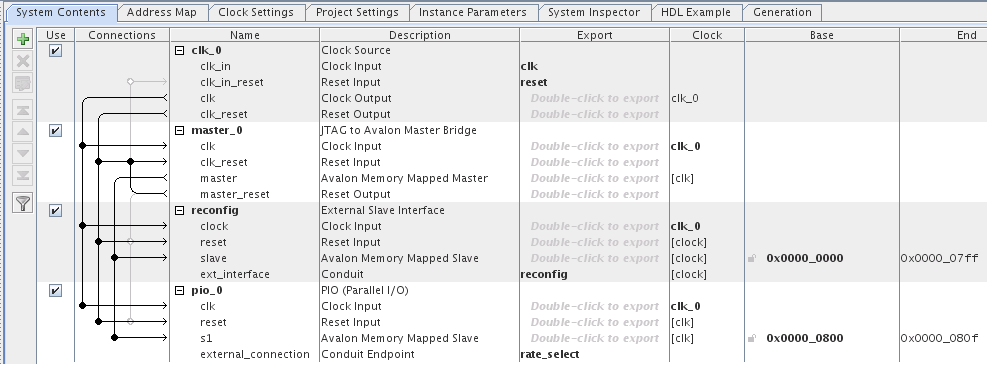

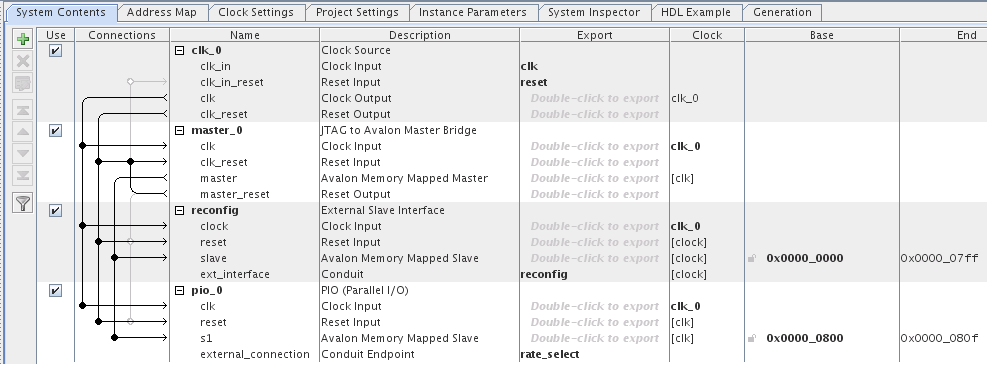

1.4.1.1. The Qsys System Components

The Qsys tool launches and shows all components used.

The Qsys system contains the following components:

- The JTAG to Avalon Master Bridge component acts as the master in the design example and is the main communication channel between the System Console tool and the external slave interface in the design. The System Console tool issues Avalon reads and writes to the Reconfiguration Controller to carry out reconfiguration of the PHY IP.

- The External Slave Interface component exports all required Avalon signals to the top-level design. With the Avalon signals exported, the Qsys system can interface with any Avalon-compliant component that resides outside of the Qsys component library.

- The Transceiver Reconfiguration Controller is an Avalon-compliant component. Therefore, the External Slave Interface component must be connected to the JTAG to Avalon Master Bridge.

- The PIO component uses external input as control bits in the system. In this design example, the PIO is connected to the rate_select port, which is used to trigger the rate change of the channel from 2500 Mbps to 5000 Mbps. The PIO connects to the JTAG to Avalon Master Bridge. You can also connect any PIO to status bits to be monitored externally.

Note: The Arria V and Cyclone V PHY IP components are not supported in the Qsys tool in the Quartus II software. To interface with an Arria V or Cyclone V PHY IP in a Qsys system, you must use an external slave interface.

Figure 2. Component Map of the Qsys System

| Name |

Component Name |

Base Address |

Description |

|---|---|---|---|

| reconfig |

External Slave Interface |

0x000 |

Exports Avalon signals to interface with the Reconfiguration Controller |

| pio_0 |

PIO (Parallel I/O) |

0x800 |

Export the rate_select port for TX PLL selection |

Related Information