# USB 3.0 INTERNAL CONNECTOR AND CABLE SPECIFICATION

Revision 1.0 August 20, 2010

©2007- 2010 Intel Corporation—All rights reserved.

#### Legal Disclaimers

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE.

A COPYRIGHT LICENSE IS HEREBY GRANTED TO REPRODUCE AND DISTRIBUTE THIS SPECIFICATION FOR INTERNAL USE ONLY. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY OTHER INTELLECTUAL PROPERTY RIGHTS IS GRANTED OR INTENDED HEREBY.

INTEL CORPORATION AND THE AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF PROPRIETARY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS DOCUMENT AND THE SPECIFICATION. INTEL CORPORATION AND THE AUTHORS OF THIS SPECIFICATION ALSO DO NOT WARRANT OR REPRESENT THAT SUCH IMPLEMENTATION(S) WILL NOT INFRINGE SUCH RIGHTS.

ALL SUGGESTIONS OR FEEDBACK RELATED TO THIS SPECIFICATION BECOME THE PROPERTY OF INTEL CORPORATION UPON SUBMISSION.

INTEL CORPORATION MAY MAKE CHANGES TO SPECIFICATIONS, PRODUCT DESCRIPTIONS, AND PLANS AT ANY TIME, WITHOUT NOTICE.

**Notice:** Implementations developed using the information provided in this specification may infringe the patent rights of various parties including the parties involved in the development of this specification. Except as expressly granted hereunder, no license, express or implied, by estoppel or otherwise, to any intellectual property rights (including without limitation rights under any party's patents) are granted herein.

All product names are trademarks, registered trademarks, or service marks of their respective owners

# **REVISION HISTORY**

| Date       | Specification Version | Revisions                                                   |

|------------|-----------------------|-------------------------------------------------------------|

| 05-22-2009 | Rev. 0.0              | Initial Draft                                               |

| 06-30-2009 | Rev. 0.2              | Rev 0.2, electrical specification.                          |

| 08-16-2009 | Rev. 0.4              | Rev 0.4, electrical specification, mechanical specification |

| 12-12-2009 | Rev 0.8               | Rev 0.8 Modified electrical specification                   |

| 02-1-2010  | Rev 0.9               | Editorial                                                   |

| 05-1-2010  | Rev 0.95              | Fixed a typo in Figure 3-1                                  |

| 07-20-2010 | Rev 1.0 Draft         | Slight changes in electrical spec and drawing cleanups      |

| 08-20-2010 | Rev 1.0               | Insertion loss is changed from 2.5 db to 3.0 dB at 2.5 GHz  |

## **CONTENTS**

| 1. | In  | ntroduction                                                      | 7  |

|----|-----|------------------------------------------------------------------|----|

| 2. | El  | lectrical Specifications                                         | 8  |

| 2  | 2.1 | Signal Descriptions and Pin Assignments                          | 8  |

| 2  | 2.2 | Signal Integrity Requirements                                    | 11 |

|    | 2   | 2.2.1 Mated Connector                                            | 11 |

|    | 2   | 2.2.2 Mated Cable Assemblies                                     |    |

|    |     | 2.2.2.1 Differential Insertion Loss                              |    |

|    |     | 2.2.2.2 Differential Near-End Crosstalk between SuperSpeed Pairs | 13 |

|    |     | 2.2.2.3 Differential Far-end Crosstalk between SuperSpeed Pairs  |    |

|    |     | 2.2.2.4 Intra-Pair Skew                                          | 14 |

| 2  | 2.3 | Connector Via and Anti Pad Requirements                          | 14 |

| 2  | 2.4 | EMI Requirement                                                  | 16 |

| 2  | 2.5 | Other Electrical Requirements                                    | 16 |

| 3. | M   | Iechanical Specifications                                        | 17 |

| 3  | 3.1 | Header                                                           | 17 |

| 3  | 3.2 | Cable Plug                                                       | 18 |

| 3  | 3.3 | Cable                                                            | 20 |

| 3  | 3.4 | Mechanical Requirements and Tests                                | 21 |

| 3  | 3.5 | System Shock and Vibration requirements                          | 21 |

| 3  | 3.6 | Additional Requirements                                          | 22 |

## 1. Introduction

Desktop PC's typically have USB ports on the front-panel of the enclosure. Internal cable assemblies are usually used to connect the external USB ports on the front panel to the motherboard.

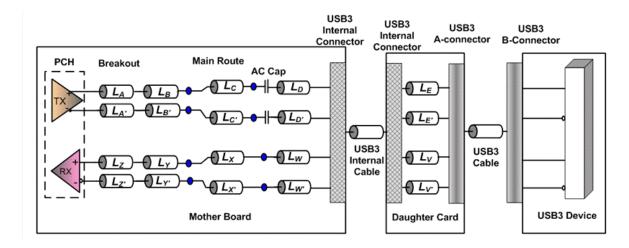

The internal cable assembly may connect the motherboard to the external USB ports via a daughter card, bringing the necessary signals to the USB ports. The USB standard-A connector is mounted on the daughter card, accessible to an end-user from the front of a chassis. Figure 1-1 illustrated the USB 3.0 interconnect topology.

Figure 1-1: USB 3.0 interconnect topology with internal cable

Alternatively, the internal cable assembly may directly connect to the external USB ports, the Standard-A connectors, without the daughter card.

This document describes the internal cable interface for USB 3.0 implementation in desktop. It focuses on the electrical and mechanical requirements of the connector and cable assembly. The detailed daughter card or direct-cable implementation is out of the scope of this documentation.

## 2. ELECTRICAL SPECIFICATIONS

The Electrical Specification describes the cable connector interface pin out, signal integrity, and other electrical requirements.

## 2.1 Signal Descriptions and Pin Assignments

For the purpose of discussion, it is assumed that the front-panel implementation involves a daughter card. The USB 3.0 internal cable connector A, or USB3 ICC A, is mounted on the motherboard, while the USB 3.0 internal cable connector B, or USB3 ICC B, is mounted on the daughter card.

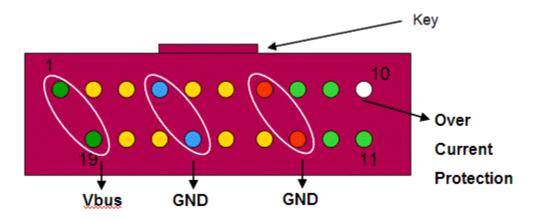

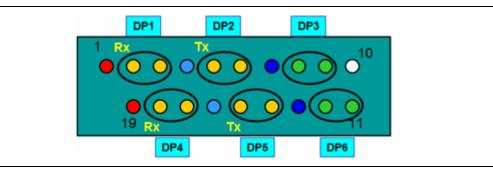

Figure 2-1 illustrates the USB3 ICC pin numbering. Note that the connector included two USB ports.

Figure 2-1: USB3 ICC pin numbering

Users may choose to include more or less USB ports by expanding or reducing the pin and wire counts. This document covers only the base unit with two USB ports.

The connector signal names and pin descriptions are given in Table 2-1 and Table 2-2, respectively for the motherboard (A-side) and the daughter card (B-side) connector. The pin connections diagram is given in Table 2-3.

Table 2-1: USB3 ICC A Pin Assignment and Description

| Pin No. | Signal        | Description                        |

|---------|---------------|------------------------------------|

| 1       | Vbus          | Power                              |

| 2       | IntA_P1_SSRX- | USB3 ICC Port1 SuperSpeed Rx-      |

| 3       | IntA_P1_SSRX+ | USB3 ICC Port1 SuperSpeed Rx+      |

| 4       | GND           | GND                                |

| 5       | IntA_P1_SSTX- | USB3 ICC Port1 SuperSpeed Tx-      |

| 6       | IntA_P1_SSTX+ | USB3 ICC Port1 SuperSpeed Tx+      |

| 7       | GND           | GND                                |

| 8       | IntA_P1_D-    | USB3 ICC Port1 D- (USB2 Signal D-) |

| 9       | IntA_P1_D+    | USB3 ICC Port1 D+ (USB2 Signal D+) |

| 10      | ID            | Over Current Protection            |

| 11      | IntA_P2_D+    | USB3 ICC Port2 D+ (USB2 Signal D+) |

| 12      | IntA_P2_D-    | USB3 ICC Port2 D- (USB2 Signal D-) |

| 13      | GND           | GND                                |

| 14      | IntA_P2_SSTX+ | USB3 ICC Port2 SuperSpeed Tx+      |

| 15      | IntA_P2_SSTX- | USB3 ICC Port2 Super Speed Tx-     |

| 16      | GND           | GND                                |

| 17      | IntA_P2_SSRX+ | USB3 ICC Port2 SuperSpeed Rx+      |

| 18      | IntA_P2_SSRX- | USB3 ICC Port2 SuperSpeed Rx-      |

| 19      | Vbus          | Power                              |

Table 2-2: USB3 ICC B Pin Assignment and Description

| Pin No. | Signal        | Description                       |

|---------|---------------|-----------------------------------|

| 1       | Vbus          | Power                             |

| 2       | IntA_P2_SSRX- | USB3 ICC Port2 SuperSpeed Rx-     |

| 3       | IntA_P2_SSRX+ | USB3 ICC Port2 SuperSpeed Rx+     |

| 4       | GND           | GND                               |

| 5       | IntA_P2_SSTX- | USB3 ICC Port2 SuperSpeed Tx-     |

| 6       | IntA_P2_SSTX+ | USB3 ICC Port2 SuperSpeed Tx+     |

| 7       | GND           | GND                               |

| 8       | IntA_P2_D-    | USB3 ICC Port2 D- (USB D-)        |

| 9       | IntA_P2_D+    | USB3 ICC Port2 D+ (USB D+)        |

| 10      | ID            | Over Current Protection           |

| 11      | IntA_P1_D+    | USB3 ICC Port1 D+ (USB Signal D+) |

| 12      | IntA_P1_D-    | USB3 ICC Port1 D- (USB Signal D-) |

| 13      | GND           | GND                               |

| 14 | IntA_P1_SSTX+ | USB3 ICC Port1 SuperSpeed Tx+ |

|----|---------------|-------------------------------|

| 15 | IntA_P1_SSTX- | USB3 ICC Port1 SuperSpeed Tx- |

| 16 | GND           | GND                           |

| 17 | IntA_P1_SSRX+ | USB3 ICC Port1 SuperSpeed Rx+ |

| 18 | IntA_P1_SSRX- | USB3 ICC Port1 SuperSpeed Rx- |

| 19 | Vbus          | Power                         |

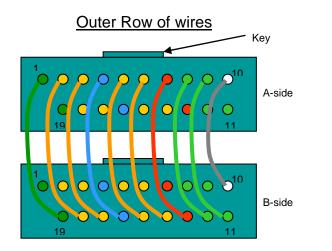

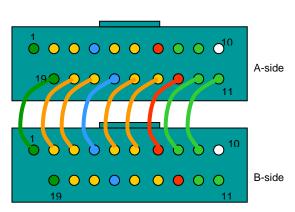

Table 2-3: Pin connection diagram and table

Inner Row of wires

| Pin No.<br>Motherboard<br>header | Cable                             | Pin No. Daughter<br>card header |

|----------------------------------|-----------------------------------|---------------------------------|

| 1                                | Power, Discrete wire              | 19                              |

| 2                                | USB3 SuperSpeed Rx, differential  | 18                              |

| 3                                | shielded pair                     | 17                              |

| 4                                | GND, Drain wire                   | 16                              |

| 5                                | USB3 SuperSpeed Tx, differential  | 15                              |

| 6                                | shielded twist pair               | 14                              |

| 7                                | GND, Discrete wire                | 13                              |

| 8                                | USB2 differential wire            | 12                              |

| 9                                |                                   | 11                              |

| 10                               | Over current protection, Discrete | 10                              |

| 11                               | USB differential wire             | 9                               |

| 12                               |                                   | 8                               |

| 13                               | GND, Discrete wire                | 7                               |

| 14                               | USB3 SuperSpeed Tx, differential  | 6                               |

| 15                               | shielded pair.                    | 5                               |

| 16                               | GND, Drain wire                   | 4                               |

| 17                               | USB3 Super speed Rx, differential | 3                               |

| 18                               | shielded pair.                    | 2                               |

| 19                               | Power, Discrete wire              | 1                               |

## 2.2 Signal Integrity Requirements

This section specifies the signal integrity requirements for the USB 3.0 internal SuperSpeed signals. Unless otherwise specified, the requirements are for the entire signal path of the mated cable assembly, from the connector through-holes on the motherboard to the connector through-holes on the daughter card, not including PCB traces, as illustrated in Figure 2-1; the measurement is between TP1 (test point 1) and TP2 (test point 2).

Figure 2-1: Illustration of Test Points for a Mated Cable Assembly

For proper measurements, the connectors shall be mounted on a test fixture. The test fixture shall have uncoupled access traces from SMA to the test points, preferably with  $50 \Omega + /-7\% \Omega$  single-ended characteristic impedance. All non-ground pins that are adjacent but not connected to measurement ports shall be terminated with  $50 \Omega$  loads.

The test fixture shall at least have the *thru* calibration structure to remove the fixture loss effect in the frequency domain measurement. For time domain measurements, removing the fixture loss effect is not required. However, the insertion loss of the thru must be no greater than 1.7 dB. In addition, the fixture shall also have an appropriate structure to verify the risetime entering the connector under test.

Note that signals shall be launched into the connector from the bottom of the PCB to minimize the through-hole stub effect.

#### 2.2.1 Mated Connector

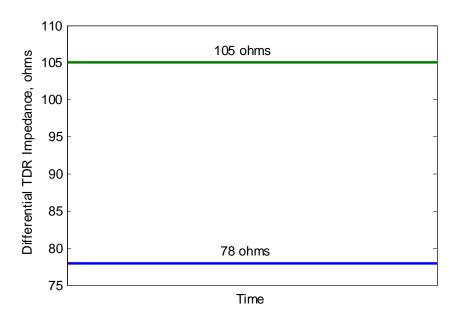

The differential impedance of a mated connector shall be within 78 ohm and 105 ohm, as seen from a 50 ps (20%-80%) risetime of a differential TDR at the connector. Figure 2-2 illustrates the impedance limits of a mated connector. The impedance profile of a mated connector must fall within the limits shown in Figure 2-2. Note that the impedance profile of the mated connector is defined from the receptacle footprints through the plug cable termination area.

Figure 2-2: Impedance Limits of a Mated Connector

#### 2.2.2 Mated Cable Assemblies

A mated cable assembly refers to a cable assembly mated with the corresponding receptacles mounted on a test board fixture at the both ends of the cable.

#### 2.2.2.1 Differential Insertion Loss

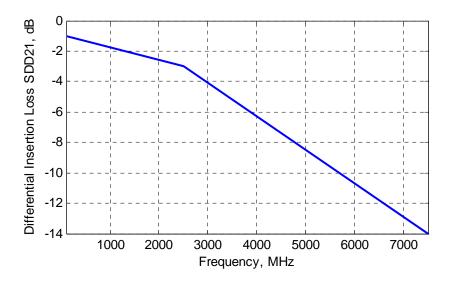

The differential insertion loss, SDD21, measures the differential signal energy transmitted through the mated cable assembly. Figure 2-3 shows the differential insertion loss limit, defined by the following vertices: (100 MHz, -1 dB), (2.5GHz, -3.0 dB), and (7.5GHz, -14.0 dB). The measured differential insertion loss of a mated cable assembly must be above or on the differential insertion loss limit. Note again that the requirement is for the mated cable assembly only, not including fixture; the simple thru, or more sophisticated TRL calibration may be used to remove the fixturing effect.

Figure 2-3: Differential Insertion Loss Requirement

#### 2.2.2.2 Differential Near-End Crosstalk between SuperSpeed Pairs

The differential crosstalk measures the unwanted coupling between differential pairs. Figure 2-4 illustrated the differential pair coupling diagram.

Figure 2-4: Differential pair coupling diagram

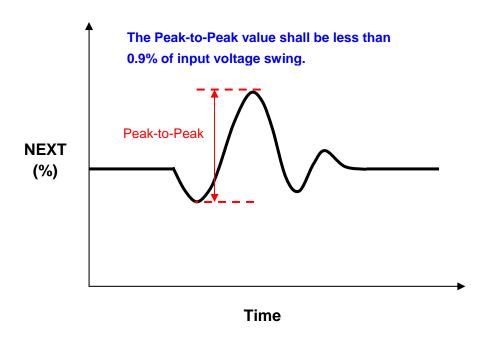

The differential near-end crosstalk is required for the TX-RX pairs DP1-DP2, DP4-DP5 and DP2-DP4. The differential near-end crosstalk shall be measured in the time-domain with TDT in differential mode and the risetime shall be verified to be 50 ps (20-80%) at the connector under test. The measured crosstalk shall be no greater than 0.9%, peak to peak, as illustrated in Figure 2-5.

Figure 2-5: Illustration of peak-to-peak crosstalk

#### 2.2.2.3 Differential Far-end Crosstalk between SuperSpeed Pairs

The differential far-end crosstalk is required for all the TX-to-TX and RX-to-RX SuperSpeed pairs. The differential far-end crosstalk shall be measured in the time-domain with TDT in differential mode and the risetime shall be verified to be 50 ps (20-80%) entering the connector under test. The measured crosstalk shall be no greater than 1.85%, peak to peak.

#### 2.2.2.4 Intra-Pair Skew

The intra-pair skew of the mated cable assembly shall be controlled to be less than 15 ps. The measurement shall be done with a TDT in differential mode for each of the SuperSpeed pairs with a 50 ps (20-80%) risetime. The propagation delay of each line in a differential pair at the 50% crossing shall be measured and the delay difference reported as the intra-pair skew.

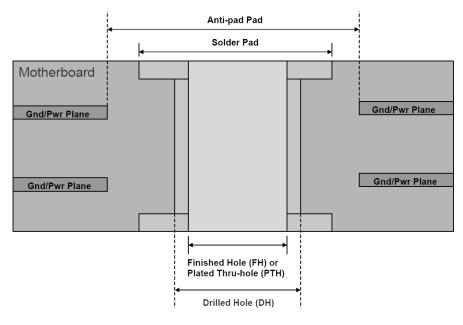

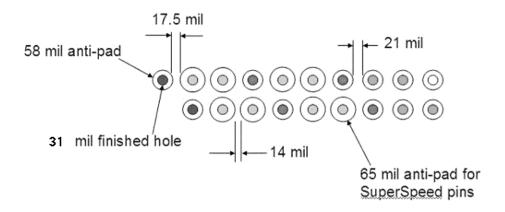

## 2.3 Connector Via and Anti Pad Requirements

Since the impedance control of the USB 3.0 internal connector is critical to USB 3.0 channel performance, it is important to meet connector via requirements shown in Figure 2-6.

## **Definition of Terminology**

| FH or PTH (Finished Hole) | Solder Pad          | Anti Pad Size                                                                   |

|---------------------------|---------------------|---------------------------------------------------------------------------------|

| 0.8 mm (31 mils)          | <=1.17 mm (46 mils) | >=1.65 mm (65 mil) for<br>SuperSpeed pins<br>1.47 mm (58 mil) for other<br>pins |

Figure 2-6: Connector Via and Anti-Via requirements

Signals shall be launched into the connector from the bottom of the PCB to minimize the throughhole stub effect. Smaller hole and pad sizes are preferred for signal integrity purposes, as long as board assembly DFM (Design for Manufacturing) rules allow.

## 2.4 EMI Requirement

Host systems that implement USB 3.0 front panel connector and cable assembly must meet the relevant FCC EMI requirements.

## 2.5 Other Electrical Requirements

Table 2-4 lists the other electrical requirements that the cable assembly must meet, including the low-level contact resistance and current rating.

**Table 2-4: Other Electrical Requirements**

| Parameter                 | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Requirements                                                                                                                                                                           |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contact Resistance (LLCR) | EIA 364- 23B Subject mated contacts assembled in housing to 20 mV max open circuit at 100 mA max                                                                                                                                                                                                                                                                                                                                                                                                    | Initial: $30~\text{m}\Omega$ max for a mated connector Final (after stress): $50~\text{m}\Omega$ max (allowable resistance change: $20~\text{m}\Omega$ )                               |

| Current rating            | <ol> <li>EIA 364-70 method 2</li> <li>Test the mated cable assembly:         <ol> <li>The sample size is a minimum of three mated connectors.</li> <li>The sample shall be soldered on a PCB board with the appropriate footprint.</li> <li>Wire all the voltage and all the ground pins in a series circuit.</li> <li>A thermocouple of 30 AWG or less shall be placed to as close to the mating contact as possible.</li> <li>Conduct a temperature rise vs. current test.</li> </ol> </li> </ol> | 0.5 A per pin minimum for signals;<br>1.5 A per pin minimum for VBUS.<br>The temperature rise above ambient<br>shall not exceed 30 °C. The ambient<br>condition is still air at 25 °C. |

## 3. MECHANICAL SPECIFICATIONS

The cable assembly mechanical specification defines the cable assembly interface dimensions, header footprint, and mechanical performance requirements, such as durability, mating/unmating forces.

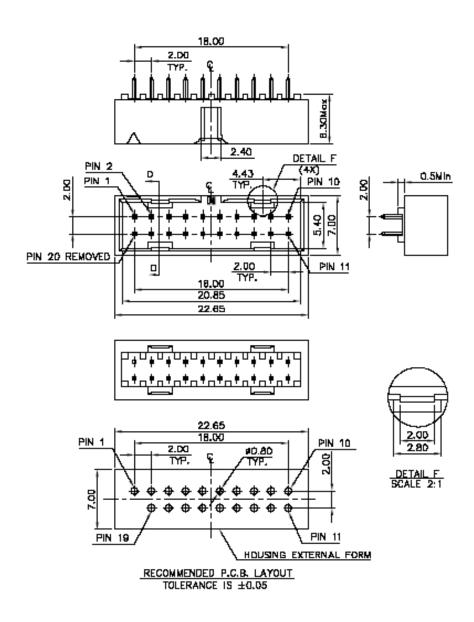

## 3.1 Header

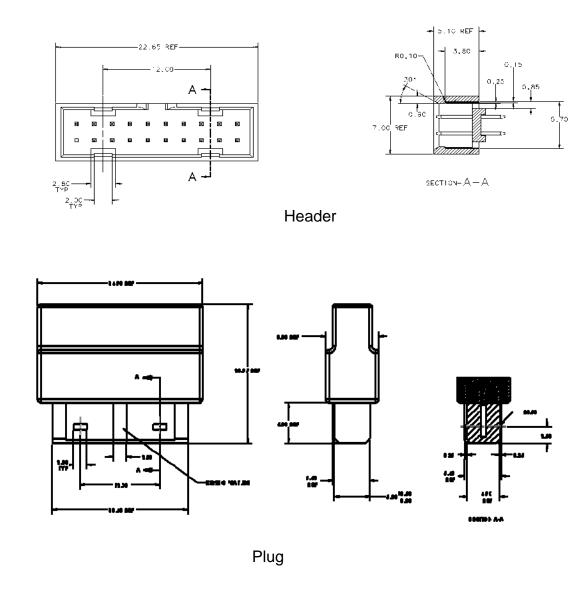

The USB 3.0 Internal cable assembly connects the motherboard and daughter card together via connectors. The vertical connector mounted on the PCB is referred to as the header. Figure 3-1 shows the header mechanical interface dimensions.

Figure 3-1: Header interface dimensions

## 3.2 Cable Plug

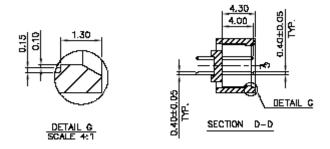

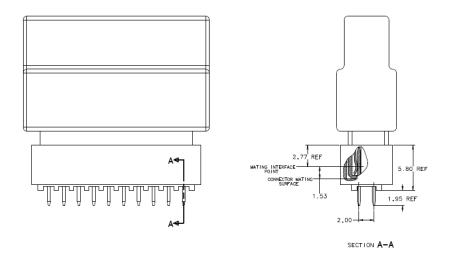

Figure 3-2 shows some reference dimensions for the header and outline dimensions for the cable plug. The mating interface dimensions of the plug can be derived from header dimensions. Note that the indent features defined in the header housing are for mechanical retention when the plug is mated with the header. Figure 3-3 shows the nominal contact point location when the plug is in the header.

Figure 3-2: Header and cable plug dimensions

Figure 3-3: Header and cable plug contact location

## 3.3 Cable

This specification defines only the form, fit, and function of the cable assembly. Thus, the specific cable construction is up to each connector and cable assembly manufacturer. The following cable requirements and/or guidelines apply:

- □ The maximum cable assembly length shall not exceed 457.2 mm (18"). For most small form factor systems, a 12" is recommended.

- $\Box$  To ensure the cable flexibility, the cable shall be able to be bent to a radius less than 25.4 mm (1.0").

- $\Box$  The raw cable impedance should be managed to be within 90+/-7 ohms.

## 3.4 Mechanical Requirements and Tests

*Table 3-1* lists the USB 3.0 internal cable mechanical requirements.

Table 3-1: Cable assembly mechanical requirements

| Parameter                         | Procedure                                                                                                       | Requirements                                                                                                                                        |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Mating force                      | EIA 364-13  Measure the force necessary to mate the connector assemblies at a max rate of 12.5 mm per minute.   | 35 N max                                                                                                                                            |

| Unmating force                    | EIA 364-13  Measure the force necessary to unmate the connector assemblies at a max rate of 12.5 mm per minute. | 15 N min                                                                                                                                            |

| Durability                        | EIA 364-09<br>25 cycles. Done at a max rate of 200 cycles per hour.                                             | No physical damage to any part of the connector and cable assembly.                                                                                 |

| Cable flexing                     | EIA 364-41 Condition I Dimension X=5.5x cable diameter. 50 cycles in each of two planes                         | No physical damage. No discontinuity over 1 ms during flexing.                                                                                      |

| Visual and dimensional inspection | EIA 364- 18 Visual, dimensional and functional inspection per applicable quality inspection plan.               | Meets product drawing requirements                                                                                                                  |

| Flammability                      | UL 94V-1                                                                                                        | Material certification or certificate of compliance required with each lot to satisfy the Underwriters Laboratories follow-up service requirements. |

| Lead-free soldering               |                                                                                                                 | Contact finish and header housing material be compatible with lead-free soldering process.                                                          |

Special attention shall be paid to the unmating force. Since there is no positive retention mechanism defined for the cable assembly, the unmating force between the cable connector and header is the only mechanism to retain the cable assembly during shock and vibration.

## 3.5 System Shock and Vibration requirements

The mated cable assembly shall pass the system level shock and vibration tests to be performed by system OEMs. The table below specifies the baseline shock and vibration requirements. Variation from those baseline requirements is allowed at each OEM's discretion.

**Table 3-2: Baseline Shock and Vibration Requirements**

| Test Name                                | Description                                                                                                                                                                            | Requirements                                                                                                                                                                                           |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System level<br>Shock,<br>unpackaged     | 30G trapezoidal, 170 in/second; 3 drops in each of the 6 axes.                                                                                                                         | No visible damage. No displacement of components, cable, or hardware. The product must operate normally after the completion of the stress.                                                            |

| System level<br>vibration,<br>unpackaged | Random profile: 5 Hz @ 0.001 g^2 / Hz to 20 Hz @ 0.01 g^2/Hz (slope up); 20 Hz to 500 Hz @ 0.01 g^2 / Hz (flat). Input acceleration is 2.20 g RMS. 10 minutes per axis for all 3 axes. | No visible damage. No displacement of the cable interface. No more than one intermittent failure during random vibration stress. The product must operate normally after the completion of the stress. |

## 3.6 Additional Requirements

This document does not attempt to specify all the requirements for the USB 3.0 internal connector and cable assembly. Specifying additional requirements, for example, the environmental requirements, is up to the OEMs and/or end users.