# Intel® Rack Scale Design (Intel® RSD) Architecture Specification

Software v2.4

**April 2019**

**Revision 001**

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Performance varies depending on system configuration. No computer system can be secure. Check with your system manufacturer or retailer or learn more at <a href="https://www.intel.com">www.intel.com</a>.

No license (express, implied, by estoppel, or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and no infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Copies of documents that have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>.

Intel and the Intel logo are trademarks of Intel Corporation in the United States and other countries.

\* Other names and brands may be claimed as the property of others.

Copyright © 2019, Intel Corporation. All rights reserved.

# **Contents**

| 3.2.4 Just a Bunch of Disks (JBOD) Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.0 | Introdu  | ıction   |                                                     | 11 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|----------|-----------------------------------------------------|----|

| 1.3 Intel® RSD Platform Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 1.1      | Scope    |                                                     | 11 |

| 1.3 Intel® RSD Platform Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 1.2      | Intende  | ed Audience                                         | 11 |

| 1.3.1   Major Changes in Intel® RSD v2.1   1.2     1.3.2   Major Changes in Intel® RSD v2.2   1.2     1.3.3   Major Changes in Intel® RSD v2.3   1.2     1.3.4   Major Changes in Intel® RSD v2.3   1.2     1.3.5   Major Changes in Intel® RSD v2.3   1.2     1.3.6   Architecture Terminology Definitions   1.3     1.3.7   Logical Representation of Intel® RSD v2.4   1.3     1.3.8   Management Elements of Intel® RSD POD   1.4     1.3.9   North Bound Management Hierarchy of Intel® RSD POD   1.4     1.3.1   Full Management Hierarchy of Intel® RSD POD   1.5     1.3.11   Full Management Hierarchy of Intel® RSD POD   1.5     1.3.12   Interfaces of Intel® RSD POD   1.6     1.3.13   Mapping POD Software to POD Architecture Layers   1.7     1.3.14   Intel® RSD Pot Container Options   1.7     1.3.15   Intel® RSD Pot Software to POD Architecture Layers   1.7     1.3.14   Intel® RSD Pot Software to POD Architecture Layers   1.7     1.5   Intel® RSD Platform Software Components   1.8     1.6   Intel® RSD Platform Software Components   1.8     1.7   Conventions   1.8     1.8   Notes and Symbol Convention   1.8     1.9   Acronym Definitions   1.9     1.0   References to More Information   2.1     2.2   Intel® RSD Platform Requirements Summary   2.3     3.1   Intel® RSD Platform Requirements Summary   2.3     3.2   Generic Intel® RSD Platform Requirements Summary   2.3     3.2   Shared or Highly Efficient Power Supply   3.0     3.2.1   Rack Must Have One or More Logical Pooled System Management Engine (PSME)   3.2     3.2.2   Shared or Highly Efficient Cooling   3.1     3.2.3   Shared or Highly Efficient Power Supply   3.0     3.2.4   Just a Bunch of Disks (JBOD) Support   3.1     3.2.5   Compute Module with Local Boot Drive   3.1     3.2.6   At Least One Intel® RSD Compute Module in a POD   3.2     3.2.1   Rack Must Have One or More Logical Pooled System Management Engine (PSME)   3.2     3.2.2   Platform Support for PNC Capability Independence   3.1     3.2.3   Shared or Highly Efficient Cooling   3.2     3.2.1   PODM Support for |     | 1.3      |          |                                                     |    |

| 1.3.2 Major Changes in Intel® RSD v2.2   12   1.3.3 Major Changes in Intel® RSD v2.3   12   1.3.4 Major Changes in Intel® RSD v2.3   12   1.3.5 Major Changes in Intel® RSD v2.4   13   1.3.5 Major Changes in Intel® RSD v2.4   13   1.3.6 Architecture Terminology Definitions   13   1.3.7 Logical Representation of Intel® RSD v2.4   13   1.3.8 Management Elements of Intel® RSD POD   14   1.3.8 Management Elements of Intel® RSD POD   14   1.3.9 North Bound Management Hierarchy of Intel® RSD POD   15   1.3.10 Full Management Hierarchy of Intel® RSD POD   1.5   1.3.11 Full Physical Containment Hierarchy of Intel® RSD POD   1.6   1.3.12   Interfaces of Intel® RSD POD   1.6   1.3.13   Mapping POD Software to POD Architecture Layers   1.5   1.3.14   Intel® RSD POT   1.3.14   Intel® RSD POT   1.5   1.3.15   Intel® RSD POT   1.5   1.3.16   Intel® RSD POT   1.5   1.3.17   Intel® RSD POT   1.5   1.3.18   Intel® RSD POT   1.5   1.3.19   Intel® RSD POT   1.5   1.3.19   Intel® RSD Pot Mare to POD Architecture Layers   1.5   Intel® RSD Pot Intel® RSD POT   1.5   1.5   Intel® RSD Pot Interfaces of Intel® RSD Pot Intel® RSD Representation   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3   1.3    |     |          |          |                                                     |    |

| 1.3.3 Major Changes in Intel® RSD v2.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |          | 1.3.2    | ,                                                   |    |

| 1.3.4 Major Changes in Intel® RSD v.2.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |          | 1.3.3    | ,                                                   |    |

| 1.3.5       Major Changes in Intel® RSD v2.4       .13         1.3.6       Architecture Terminology Definitions       .13         1.3.7       Logical Representation of Intel® RSD POD       .14         1.3.8       Management Elements of Intel® RSD POD       .14         1.3.9       North Bound Management Hierarchy of Intel® RSD POD       .15         1.3.10       Full Management Hierarchy of Intel® RSD POD manager       .15         1.3.11       Full Physical Containment Hierarchy of Intel® RSD POD       .16         1.3.12       Interfaces of Intel® RSD POD       .16         1.3.13       Mapping POD Software to POD Architecture Layers       .17         1.3.14       Intel® RSD Platform Hardware Components       .18         1.5       Intel® RSD Platform Foftware Components       .18         1.6       Intel® RSD Platform Software Components       .18         1.6       Intel® RSD API       .18         1.7       Conventions       .18         1.8       Notes and Symbol Convention       .18         1.9       Acronym Definitions       .19         1.10       References to More Information       .21         2.0       Intel® RSD Platform Requirements Summary       .23         3.1       Intel® RSD Platform Requ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |          | 1.3.4    |                                                     |    |

| 1.3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |          | 1.3.5    |                                                     |    |

| 1.3.8   Management Elements of Intel® RSD POD.   14     1.3.9   North Bound Management Hierarchy of Intel® RSD POD.   15     1.3.10   Full Management Hierarchy of Intel® RSD POD.   16     1.3.11   Full Physical Containment Hierarchy of Intel® RSD POD.   16     1.3.12   Interfaces of Intel® RSD POD.   16     1.3.13   Mapping POD Software to POD Architecture Layers   17     1.3.14   Intel® RSD Container Options   17     1.4   Intel® RSD Platform Hardware Components   18     1.5   Intel® RSD Platform Software Components   18     1.6   Intel® RSD Platform Software Components   18     1.7   Conventions   18     1.8   Notes and Symbol Convention   18     1.9   Acronym Definitions   19     1.10   References to More Information   21     2.0   Intel® RSD Platform Requirements Summary   23     3.1   Intel® RSD Platform Requirements Summary   23     3.2   Generic Intel® RSD Platform Requirements   30     3.2   Generic Intel® RSD Platform Requirements   30     3.2.1   Rack Must Have One or More Logical Pooled System Management Engine (PSME)   Software   31     3.2.2   Shared or Highly Efficient Power Supply   30     3.2.3   Shared or Highly Efficient Cooling   31     3.2.5   Compute Module with Local Boot Drive   31     3.2.6   At Least One Intel® RSD Compute Module in a POD   31     3.2.7   Compute Module Serviceability Independence   31     3.2.8   Ethernet-Based Fabric for Management and External Network Connectivity   31     3.2.9   At Least One Ethernet Switch in the POD   32     3.2.10   Network Switch Support for PNC Capabilities   32     3.2.11   Pull Report for PPC Capabilities   32     3.2.12   Pull Pull Support for PPC Capabilities   32     3.2.13   Hot-Pluggable Modules in Intel® RSD V2.3 and Above   32     3.2.15   Tower Backward-Compatibility for Intel® RSD V2.3 and Above   33     3.2.16   Intel® RSD Versions Coexistence Support within a Rack   33     10.1   Rost Pluggable Modules in Intel® RSD V2.3 and Above   33     3.2.16   Intel® RSD Versions Coexistence Support within a Rack   33     3.2.16   Intel® RS |     |          | 1.3.6    |                                                     |    |

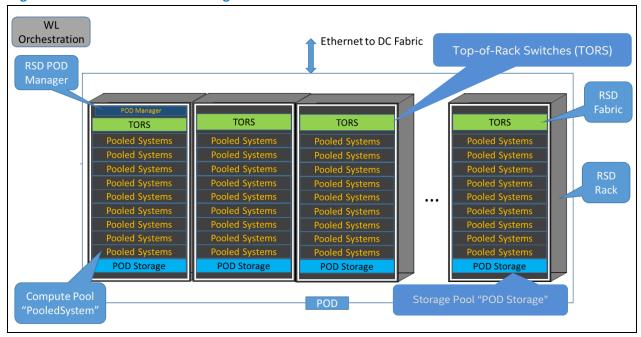

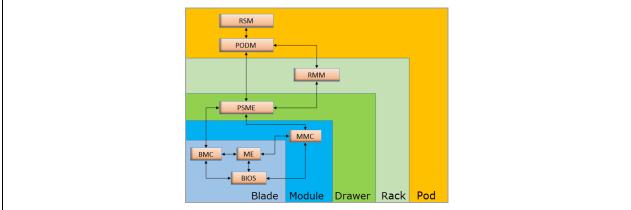

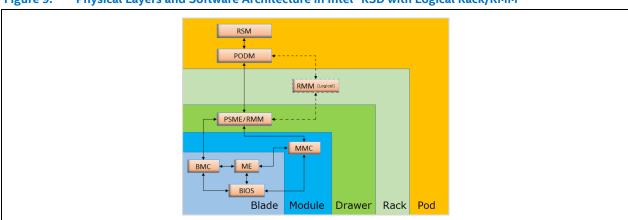

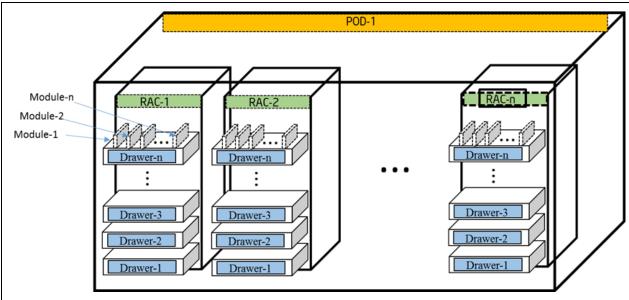

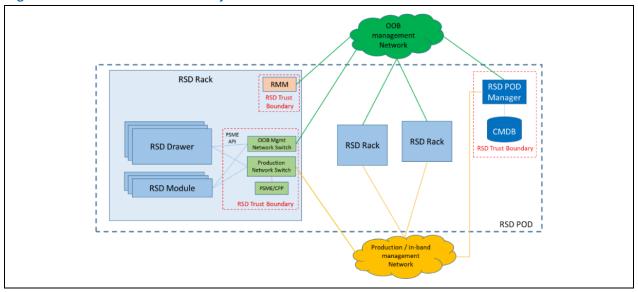

| 1.3.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |          | 1.3.7    | Logical Representation of Intel® RSD POD            | 14 |

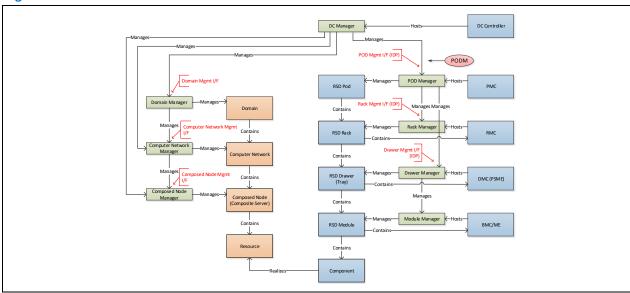

| 1.3.10   Full Management Hierarchy of Intel® RSD POD manager.   1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |          | 1.3.8    |                                                     |    |

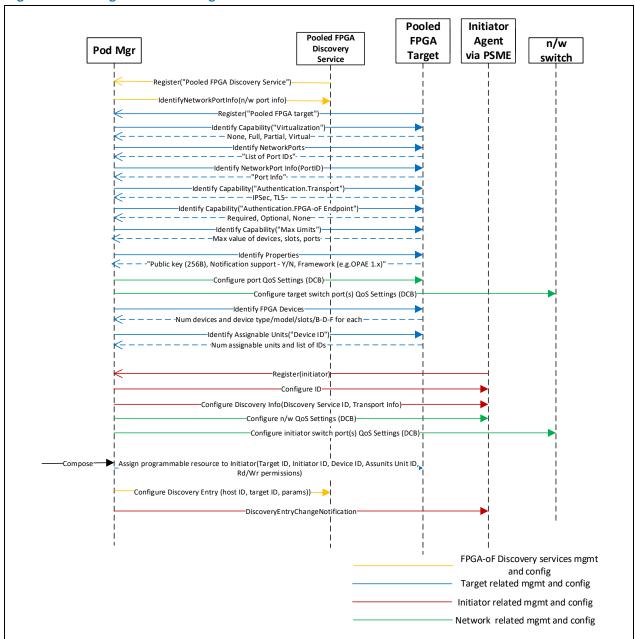

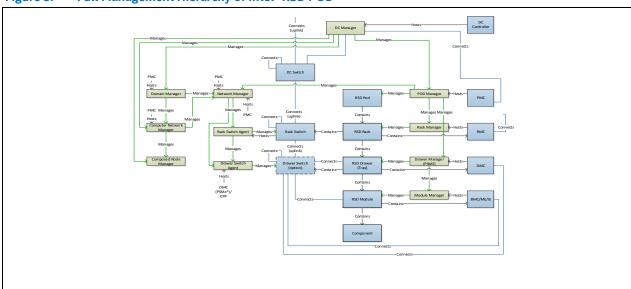

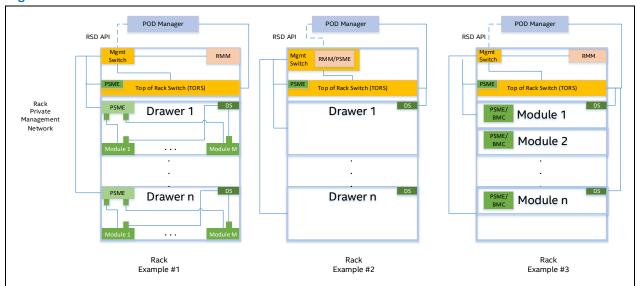

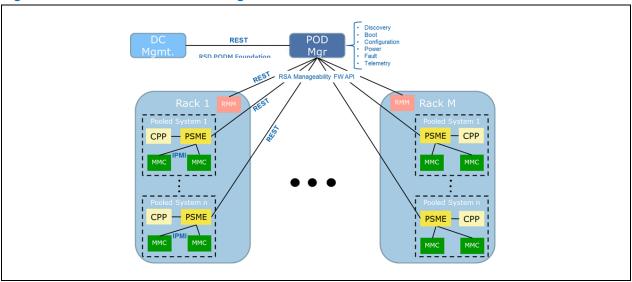

| 1.3.11   Full Physical Containment Hierarchy of Intel® RSD POD.   16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |          | 1.3.9    | North Bound Management Hierarchy of Intel® RSD POD  | 15 |

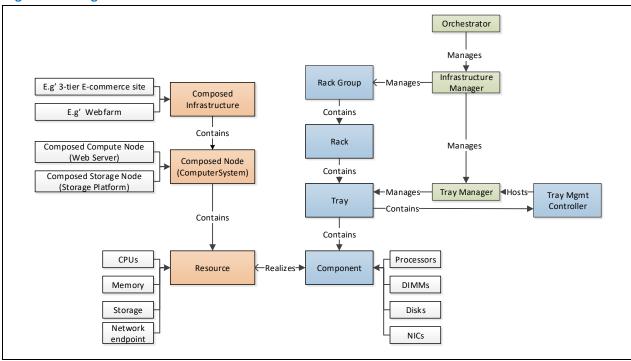

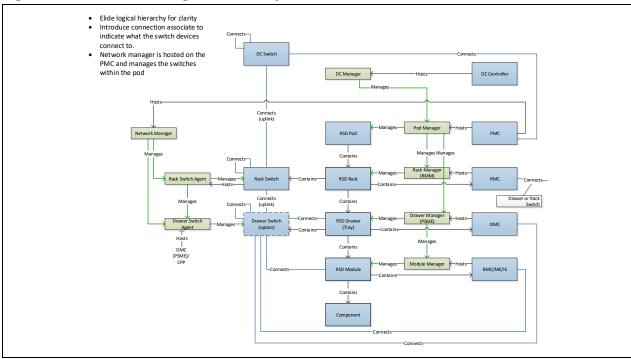

| 1.3.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |          | 1.3.10   | Full Management Hierarchy of Intel® RSD POD manager | 15 |

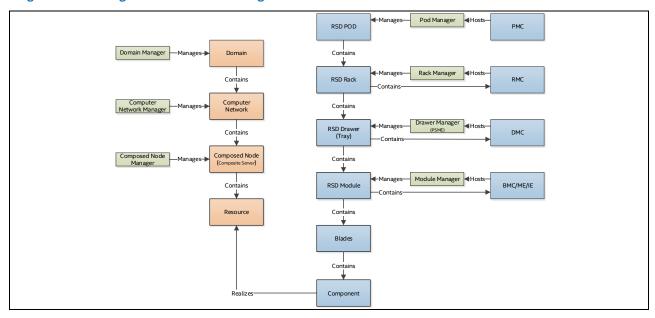

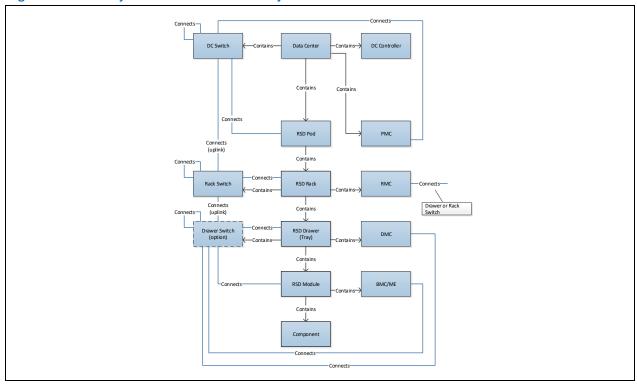

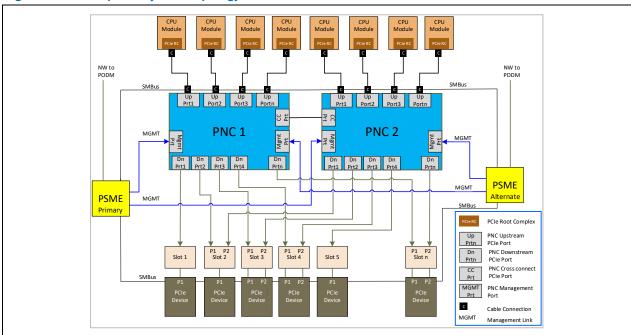

| 1.3.13       Mapping POD Software to POD Architecture Layers       17         1.3.14       Intel® RSD Container Options       17         1.4       Intel® RSD Platform Hardware Components       18         1.5       Intel® RSD Platform Software Components       18         1.6       Intel® RSD API       18         1.7       Conventions       18         1.8       Notes and Symbol Convention       18         1.9       Acronym Definitions       19         1.10       References to More Information       21         2.0       Intel® RSD Platform Requirements Summary       23         3.0       Intel® RSD Platform General Guidelines       28         3.1       Intel® RSD Platform Pequirements       28         3.1       Intel® RSD Platform Requirements       30         3.2.1       Rack Must Have One or More Logical Pooled System Management Engine (PSME)       30         3.2.2       Shared or Highly Efficient Power Supply       30         3.2.3       Shared or Highly Efficient Power Supply       30         3.2.4       Just a Bunch of Disks (JBOD) Support       31         3.2.6       At Least One Intel® RSD Compute Module in a POD       31         3.2.6       At Least One Ethernet Switch in the POD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |          | 1.3.11   |                                                     |    |

| 1.3.14       Intel® RSD Container Options       17         1.4       Intel® RSD Platform Hardware Components       18         1.5       Intel® RSD Platform Software Components       18         1.6       Intel® RSD API       18         1.7       Conventions       18         1.8       Notes and Symbol Convention       18         1.9       Acronym Definitions       19         1.10       References to More Information       21         2.0       Intel® RSD Platform Requirements Summary       23         3.0       Intel® RSD Platform Requirements Summary       23         3.1       Intel® RSD Platform General Guidelines       28         3.1       Intel® RSD Platform Requirements       30         3.2       Generic Intel® RSD Platform Requirements       30         3.2.1       Rack Must Have One or More Logical Pooled System Management Engine (PSME)       30         3.2.2       Shared or Highly Efficient Power Supply       30         3.2.3       Shared or Highly Efficient Cooling       31         3.2.4       Just a Bunch of Disks (JBOD) Support       31         3.2.5       Compute Module Serviceability Independence       31         3.2.6       At Least One Intel® RSD Compute Module in a POD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |          | 1.3.12   |                                                     |    |

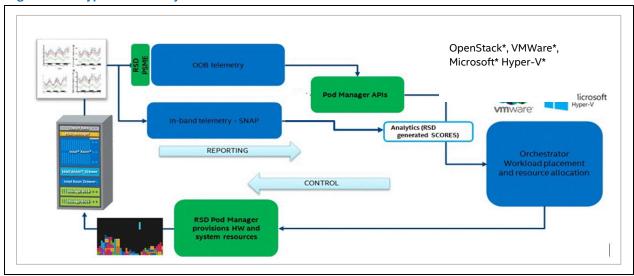

| 1.4       Intel® RSD Platform Hardware Components       18         1.5       Intel® RSD Platform Software Components       18         1.6       Intel® RSD API       18         1.7       Conventions       18         1.8       Notes and Symbol Convention       18         1.9       Acronym Definitions       19         1.10       References to More Information       21         2.0       Intel® RSD Platform Requirements Summary       23         3.0       Intel® RSD Platform General Guidelines       28         3.1       Intel® RSD Platform Power-on Flow       28         3.2       Generic Intel® RSD Platform Requirements       30         3.2.1       Rack Must Have One or More Logical Pooled System Management Engine (PSME)         Software       30         3.2.2       Shared or Highly Efficient Power Supply       30         3.2.3       Shared or Highly Efficient Cooling       31         3.2.4       Just a Bunch of Disks (JBOD) Support       31         3.2.5       Compute Module with Local Boot Drive       31         3.2.6       At Least One Intel® RSD Compute Module in a POD       31         3.2.7       Compute Module Serviceability Independence       31         3.2.9       At                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |          | 1.3.13   |                                                     |    |

| 1.5       Intel® RSD Platform Software Components       18         1.6       Intel® RSD API       18         1.7       Conventions       18         1.8       Notes and Symbol Convention       18         1.9       Acronym Definitions       19         1.10       References to More Information       21         2.0       Intel® RSD Platform Requirements Summary       23         3.0       Intel® RSD Platform General Guidelines       28         3.1       Intel® RSD Platform Power-on Flow       28         3.2       Generic Intel® RSD Platform Requirements       30         3.2.1       Rack Must Have One or More Logical Pooled System Management Engine (PSME)       30         3.2.2       Shared or Highly Efficient Power Supply       30         3.2.3       Shared or Highly Efficient Cooling       31         3.2.4       Just a Bunch of Disks (JBOD) Support       31         3.2.5       Compute Module with Local Boot Drive       31         3.2.6       At Least One Intel® RSD Compute Module in a POD       31         3.2.7       Compute Module Serviceability Independence       31         3.2.8       Ethernet-Based Fabric for Management and External Network Connectivity       31         3.2.1       Network Switc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |          | 1.3.14   | Intel® RSD Container Options                        | 17 |

| 1.6       Intel® RSD API       18         1.7       Conventions       18         1.8       Notes and Symbol Convention       18         1.9       Acronym Definitions       19         1.10       References to More Information       21         2.0       Intel® RSD Platform Requirements Summary       23         3.0       Intel® RSD Platform General Guidelines       28         3.1       Intel® RSD Platform Power-on Flow       28         3.2       Generic Intel® RSD Platform Requirements       30         3.2.1       Rack Must Have One or More Logical Pooled System Management Engine (PSME)         Software       30         3.2.2       Shared or Highly Efficient Power Supply       30         3.2.3       Shared or Highly Efficient Cooling       31         3.2.4       Just a Bunch of Disks (JBOD) Support       31         3.2.5       Compute Module with Local Boot Drive       31         3.2.6       At Least One Intel® RSD Compute Module in a POD       31         3.2.7       Compute Module Serviceability Independence       31         3.2.8       Ethernet-Based Fabric for Management and External Network Connectivity       31         3.2.9       At Least One Ethernet Switch in the POD       32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 1.4      | Intel® R | SD Platform Hardware Components                     | 18 |

| 1.7       Conventions       18         1.8       Notes and Symbol Convention       18         1.9       Acronym Definitions       19         1.10       References to More Information       21         2.0       Intel® RSD Platform Requirements Summary       23         3.0       Intel® RSD Platform General Guidelines       28         3.1       Intel® RSD Platform Power-on Flow       28         3.2       Generic Intel® RSD Platform Requirements       30         3.2.1       Rack Must Have One or More Logical Pooled System Management Engine (PSME)         Software       30         3.2.2       Shared or Highly Efficient Power Supply       30         3.2.3       Shared or Highly Efficient Power Supply       30         3.2.4       Just a Bunch of Disks (JBOD) Support       31         3.2.5       Compute Module with Local Boot Drive       31         3.2.6       At Least One Intel® RSD Compute Module in a POD       31         3.2.7       Compute Module Serviceability Independence       31         3.2.8       Ethernet-Based Fabric for Management and External Network Connectivity       31         3.2.9       At Least One Ethernet Switch in the POD       32         3.2.10       Network Switch Support for Network Software Agen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 1.5      | Intel® R | SD Platform Software Components                     | 18 |

| 1.8       Notes and Symbol Convention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 1.6      | Intel® R | SD API                                              | 18 |

| 1.9 Acronym Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 1.7      | Conven   | itions                                              | 18 |

| 1.10 References to More Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 1.8      | Notes a  | and Symbol Convention                               | 18 |

| 1.10 References to More Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 1.9      | Acrony   | m Definitions                                       | 19 |

| 2.0       Intel® RSD Platform Requirements Summary       23         3.0       Intel® RSD Platform General Guidelines       28         3.1       Intel® RSD Platform Power-on Flow       28         3.2       Generic Intel® RSD Platform Requirements       30         3.2.1       Rack Must Have One or More Logical Pooled System Management Engine (PSME)       30         3.2.2       Shared or Highly Efficient Power Supply       30         3.2.3       Shared or Highly Efficient Cooling       31         3.2.4       Just a Bunch of Disks (JBOD) Support       31         3.2.5       Compute Module with Local Boot Drive       31         3.2.6       At Least One Intel® RSD Compute Module in a POD       31         3.2.7       Compute Module Serviceability Independence       31         3.2.8       Ethernet-Based Fabric for Management and External Network Connectivity       31         3.2.9       At Least One Ethernet Switch in the POD       32         3.2.10       Network Switch Support for Network Software Agent       32         3.2.11       PODM Support for PNC Capabilities       32         3.2.12       Platform Support for FPGAS       32         3.2.14       PDOM Backward-Compatibility for Intel® RSD v2.3 and Above       32         3.2.15       Drawer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 1.10     | •        |                                                     |    |

| 3.0Intel® RSD Platform General Guidelines283.1Intel® RSD Platform Power-on Flow283.2Generic Intel® RSD Platform Requirements303.2.1Rack Must Have One or More Logical Pooled System Management Engine (PSME)Software303.2.2Shared or Highly Efficient Power Supply303.2.3Shared or Highly Efficient Cooling313.2.4Just a Bunch of Disks (JBOD) Support313.2.5Compute Module with Local Boot Drive313.2.6At Least One Intel® RSD Compute Module in a POD313.2.7Compute Module Serviceability Independence313.2.8Ethernet-Based Fabric for Management and External Network Connectivity313.2.9At Least One Ethernet Switch in the POD323.2.10Network Switch Support for Network Software Agent323.2.11PODM Support for PNC Capabilities323.2.12Platform Support for FPGAs323.2.13Hot-Pluggable Modules in Intel® RSD Drawers323.2.14PDOM Backward-Compatibility for Intel® RSD v2.3 and Above323.2.15Drawer Backward-Compatibility for Intel® RSD v2.3 and above333.2.16Intel® RSD Versions Coexistence Support within a Rack33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0 | Intel® F | SD Platf | orm Requirements Summary                            | 23 |

| 3.2 Generic Intel® RSD Platform Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.0 |          |          |                                                     |    |

| 3.2.1 Rack Must Have One or More Logical Pooled System Management Engine (PSME) Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 3.1      | Intel® R | SD Platform Power-on Flow                           | 28 |

| 3.2.1 Rack Must Have One or More Logical Pooled System Management Engine (PSME) Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 3.2      | Generio  | : Intel® RSD Platform Requirements                  | 30 |

| 3.2.2 Shared or Highly Efficient Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |          | 3.2.1    | , , ,                                               |    |

| 3.2.3 Shared or Highly Efficient Cooling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |          |          |                                                     |    |

| 3.2.4 Just a Bunch of Disks (JBOD) Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |          | _        |                                                     |    |

| 3.2.5 Compute Module with Local Boot Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |          |          |                                                     |    |

| 3.2.6 At Least One Intel® RSD Compute Module in a POD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |          | _        |                                                     |    |

| 3.2.7 Compute Module Serviceability Independence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |          |          |                                                     |    |