# Intel Guide for Developing Multithreaded Application

#### **Disclaimers**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

Copyright © 2011 Intel Corporation. All rights reserved

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Core Inside, i960, Intel, the Intel logo, Intel AppUp, Intel Atom, Intel Atom Inside, Intel Core, Intel Inside, the Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel Sponsors of Tomorrow, the Intel Sponsors of Tomorrow. logo, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, InTru, the InTru logo, InTru soundmark, Itanium, Itanium Inside, MCS, MMX, Moblin, Pentium, Pentium Inside, skoool, the skoool logo, Sound Mark, The Journey Inside, vPro Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

# The Authors

The Intel Guide for Developing Multithreaded Applications was written and edited by the following Intel Software **Engineering Team members:**

- Levent Akyil

- Clay Breshears

- Martyn Corden

- Julia Fedorova

- Paul Fischer

- Henry Gabb

- Jay Hoeflinger

- Richard Hubbard

- Alexey Kukanov

- Kevin O'Leary

- David Ott

- Eric Palmer

- Victoria GromovaAnton Pegushin

- Paul Petersen

- Todd Rosenquist

- Aaron Tersteeg

- Vladimir Tsymbal

- Mike Voss

- Thomas Zipplies

Visit the website for up-to-date articles: www.intel.com/software/threading-guide

#### **Optimization Notice**

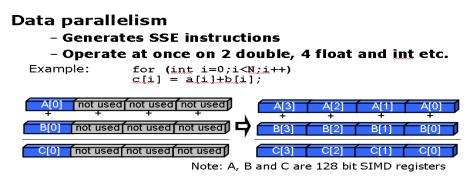

Intel<sup>®</sup> compilers, associated libraries and associated development tools may include or utilize options that optimize for instruction sets that are available in both Intel<sup>®</sup> and non-Intel microprocessors (for example SIMD instruction sets), but do not optimize equally for non-Intel microprocessors. In addition, certain compiler options for Intel compilers, including some that are not specific to Intel micro-architecture, are reserved for Intel microprocessors. For a detailed description of Intel compiler options, including the instruction sets and specific microprocessors they implicate, please refer to the "Intel<sup>®</sup> Compiler User and Reference Guides" under "Compiler Options." Many library routines that are part of Intel<sup>®</sup> compiler products are more highly optimized for Intel microprocessors than for other microprocessors. While the compilers and libraries in Intel<sup>®</sup> compiler products offer optimizations for both Intel and Intel-compatible microprocessors, depending on the options you select, your code and other factors, you likely will get extra performance on Intel microprocessors.

Intel<sup>®</sup> compilers associated libraries and associated development tools may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include Intel<sup>®</sup> Streaming SIMD Extensions 2 (Intel<sup>®</sup> SSE2), Intel<sup>®</sup> Streaming SIMD Extensions 3 (Intel<sup>®</sup> SSE3), and Supplemental Streaming SIMD Extensions 3 (Intel<sup>®</sup> SSSE3) instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors.

While Intel believes our compilers and libraries are excellent choices to assist in obtaining the best performance on Intel® and non-Intel microprocessors, Intel recommends that you evaluate other compilers and libraries to determine which best meet your requirements. We hope to win your business by striving to offer the best performance of any compiler or library; please let us know if you find we do not.

# **Table of Contents**

| Introduction                                                                                      | 3  |

|---------------------------------------------------------------------------------------------------|----|

| Predicting and Measuring Parallel Performance                                                     | 5  |

| Loop Modifications to Enhance Data-Parallel Performance                                           | .9 |

| Granularity and Parallel Performance                                                              | 14 |

| Load Balance and Parallel Performance                                                             | 20 |

| Expose Parallelism by Avoiding or Removing Artificial Dependencies                                | 24 |

| Using Tasks Instead of Threads                                                                    | 27 |

| Exploiting Data Parallelism in Ordered Data Streams                                               | 30 |

| Using AVX without Writing AVX Code                                                                | 35 |

| Managing Lock Contention: Large and Small Critical Sections                                       | 41 |

| Use Synchronization Routines Provided by the Threading API Rather than Hand-Coded Synchronization | 45 |

| Choosing Appropriate Synchronization Primitives to Minimize Overhead                              | 48 |

| Use Non-blocking Locks When Possible                                                              | 52 |

| Avoiding Heap Contention Among Threads                                                            | 55 |

| Use Thread-local Storage to Reduce Synchronization                                                | 60 |

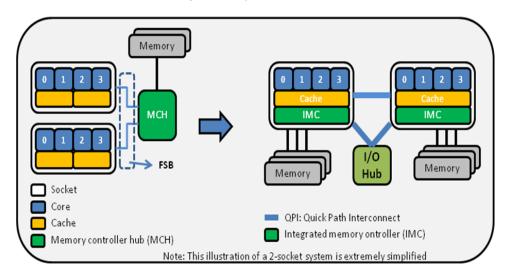

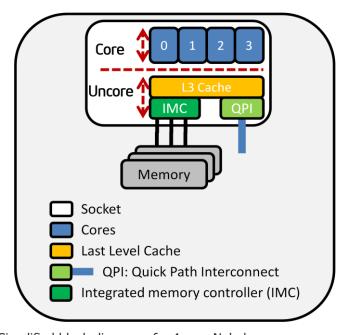

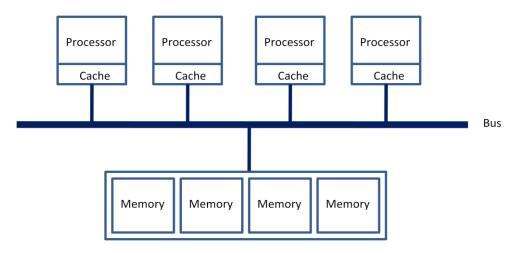

| Detecting Memory Bandwidth Saturation in Threaded Applications64                |

|---------------------------------------------------------------------------------|

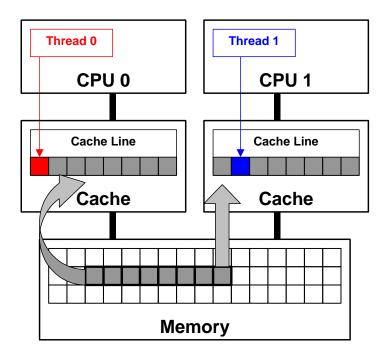

| Avoiding and Identifying False Sharing Among Threads 68                         |

| Optimizing Applications for NUMA73                                              |

| Automatic Parallelization with Intel® Compilers78                               |

| Parallelism in the Intel® Math Kernel Library82                                 |

| Threading and Intel® Integrated Performance Primitives 86                       |

| Using Intel® Inspector XE 2011 to Find Data Races in Multithreaded Code92       |

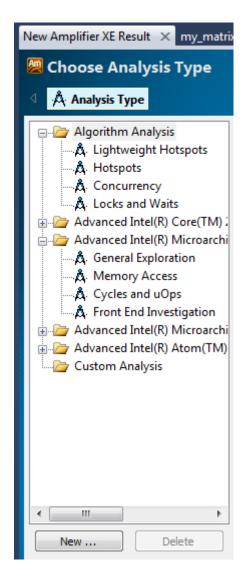

| Curing Thread Imbalance Using Intel® Parallel Amplifier98                       |

| Getting Code Ready for Parallel Execution with Intel® Parallel Composer105      |

| Optimize Data Structures and Memory Access Patterns to Improve Data Locality121 |

#### Introduction

#### **Motivation**

The objective of the *Intel® Guide for Developing Multithreaded Applications* is to provide guidelines for developing efficient multithreaded applications across Intel-based symmetric multiprocessors (SMP) and/or systems with Hyper-Threading Technology. An application developer can use the advice in this document to improve multithreading performance and minimize unexpected performance variations on current as well as future SMP architectures built with Intel® processors.

The Guide provides general advice on multithreaded performance. Hardware-specific optimizations have deliberately been kept to a minimum. Topics covering hardware-specific optimizations may be added in the future for developers willing to sacrifice portability for higher performance.

#### **Prerequisites**

Readers should have programming experience in a high-level language, preferably C, C++, and/or Fortran, though many of the recommendations in this document also apply to languages such as Java, C#, and Perl. Readers must also understand basic concurrent programming and be familiar with one or more threading methods, preferably OpenMP\*, POSIX threads (also referred to as Pthreads), or the Win32\* threading API.

### Scope

The main objective of the Guide is to provide a quick reference to design and optimization guidelines for multithreaded applications on Intel® platforms. This Guide is not intended to serve as a textbook on multithreading nor is it a porting guide to Intel platforms.

## **Organization**

The *Intel*® *Guide for Developing Multithreaded Applications* covers topics ranging from general advice applicable to any multithreading method to usage guidelines for Intel® software products to API-specific issues. Each topic in the *Intel*® *Guide for Developing Multithreaded Applications* is designed to stand on its own. However, the topics fall naturally into categories.

# Predicting and Measuring Parallel Performance

#### Abstract

Building parallel versions of software can enable applications to run a given data set in less time, run multiple data sets in a fixed amount of time, or run large-scale data sets that are prohibitive with unthreaded software. The success of parallelization is typically quantified by measuring the speedup of the parallel version relative to the serial version. In addition to that comparison, however, it is also useful to compare that speedup relative to the upper limit of the potential speedup. That issue can be addressed using Amdahl's Law and Gustafson's Law.

#### **Background**

The faster an application runs, the less time a user will need to wait for results. Shorter execution time also enables users to run larger data sets (e.g., a larger number of data records, more pixels, or a bigger physical model) in an acceptable amount of time. One computed number that offers a tangible comparison of serial and parallel execution time is *speedup*.

Simply stated, speedup is the ratio of serial execution time to parallel execution time. For example, if the serial application executes in 6720 seconds and a corresponding parallel application runs in 126.7 seconds (using 64 threads and cores), the speedup of the parallel application is 53X (6720/126.7 = 53.038).

For an application that scales well, the speedup should increase at or close to the same rate as the increase in the number of cores (threads). When increasing the number of threads used, if measured speedups fail to keep up, level out, or begin to go down, the application doesn't scale well on the data sets being measured. If the data sets are typical of actual data sets on which the application will be executed, the application won't scale well.

Related to speedup is the metric of *efficiency*. While speedup is a metric to determine how much faster parallel execution is versus serial execution, efficiency indicates how well software utilizes the computational resources of the system. To calculate the efficiency of parallel execution, take the observed speedup and divide by the number of cores used. This number is then expressed as a percentage. For example, a 53X speedup on 64 cores equates to an efficiency of 82.8% (53/64 = 0.828). This means that, on average, over the course of the execution, each of the cores is idle about 17% of the time.

#### Amdahl's Law

Before starting a parallelization project, developers may wish to estimate the amount of performance increase (speedup) that they can realize. If the percentage of serial code execution that could be executed in parallel is known (or estimated), one can use Amdahl's Law to compute an upper bound on the speedup of an application without actually writing any concurrent code. Several variations of the Amdahl's Law formula have been put forth in the literature. Each uses the percentage of (proposed) parallel execution time (pctPar), serial execution time (1 - pctPar), and the number of threads/cores (p). A simple formulation of Amdahl's Law to estimate speedup of a parallel application on p cores is given here:

$$Speedup \leq \frac{1}{(1 - pctPar) + \frac{pctPar}{p}}$$

The formula is simply the serial time, normalized to 1, divided by the estimated parallel execution time, using percentages of the normalized serial time. The parallel execution time is estimated to

be the percentage of serial execution (1 - pctPar) and the percentage of execution that can be run in parallel divided by the number of cores to be used (pctPar/p). For example, if 95% of a serial application's run time could be executed in parallel on eight cores, the estimated speedup, according to Amdahl's Law, could as much 6X (1 / (0.05 + 0.95/8) = 5.925).

In addition to the less than or equal relation ( $\leq$ ) in the formula, the formulations of Amdahl's Law assume that those computations that can be executed in parallel will be divisible by an infinite number of cores. Such an assumption effectively removes the second term in the denominator, which means that the most speedup possible is simply the inverse of the percentage of remaining serial execution.

Amdahl's Law has been criticized for ignoring real-world overheads such as communication, synchronization, and other thread management, as well as the assumption of infinite-core processors. In addition to not taking into account the overheads inherent in concurrent algorithms, one of the strongest criticisms of Amdahl's Law is that as the number of cores increases, the amount of data handled is likely to increase as well. Amdahl's Law assumes a fixed data set size for whatever number of cores is used and that the percentage of overall serial execution time will remain the same.

#### Gustafson's Law

If a parallel application using eight cores were able to compute a data set that was eight times the size of the original, does the execution time of the serial portion increase? Even if it does, it does not grow in the same proportion as the data set. Real-world data suggests that the serial execution time will remain almost constant.

Gustafson's Law, also known as *scaled speedup*, takes into account an increase in the data size in proportion to the increase in the number of cores and computes the (upper bound) speedup of the application, as if the larger data set could be executed in serial. The formula for scaled speedup is as follows:

Speedup

$$\leq p + (1-p)s$$

.

As with the formula for Amdahl's Law, p is the number of cores. To simplify the notation, s is the percentage of serial execution time in the parallel application for a given data set size. For example, if 1% of execution time on 32 cores will be spent in serial execution, the speedup of this application over the same data set being run on a single core with a single thread (assuming that to be possible) is:

$$Speedup \le 32 + (1 - 32)(0.01) = 32 - 0.31 = 31.69X.$$

Consider what Amdahl's Law would estimate for the speedup with these assumptions. Assuming the serial execution percentage to be 1%, the equation for Amdahl's Law yields 1/(0.01 + (0.99/32)) = 24.43X. This is a false computation, however, since the given percentage of serial time is relative to the 32-core execution. The details of this example do not indicate what the corresponding serial execution percentage would be for more cores or fewer cores (or even one core). If the code is perfectly scalable and the data size is scaled with the number of cores, then this percentage could remain constant, and the Amdahl's Law computation would be the predicted speedup of the (fixed-size) single-core problem on 32 cores.

On the other hand, if the total parallel application execution time is known in the 32-core case, the fully serial execution time can be calculated and the speed up for that fix-sized problem (further assuming that it could be computed with a single core) could be predicted with Amdahl's

Law on 32 cores. Assuming the total execution time for a parallel application is 1040 seconds on 32 cores, then 1% of that time would be serial only, or 10.4 seconds. By multiplying the number of seconds (1029.6) for parallel execution on 32 cores, the total amount of work done by the application takes 1029.6\*32+10.4=32957.6 seconds. The nonparallel time (10.4 seconds) is 0.032% of that total work time. Using that figure, Amdahl's Law calculates a speedup of 1/(0.00032 + (0.99968/32)) = 31.686X.

Since the percentage of serial time within the parallel execution must be known to use Gustafson's Law, a typical usage for this formula is to compute the speedup of the scaled parallel execution (larger data sets as the number of cores increases) to the serial execution of the same sized problem. From the above examples, a strict use of the data about the application executions within the formula for Amdahl's Law gives a much more pessimistic estimate than the scaled speedup formula.

#### Advice

When computing speedup, the best serial algorithm and fastest serial code must be compared. Frequently, a less than optimal serial algorithm will be easier to parallelize. Even in such a case, it is unlikely that anyone would use serial code when a faster serial version exists. Thus, even though the underlying algorithms are different, the best serial run time from the fastest serial code must be used to compute the speedup for a comparable parallel application.

When stating a speedup value, a multiplier value should be used. In the past, the speedup ratio has been expressed as a percentage. In this context, using percentages can lead to confusion. For example, if it were stated that a parallel code is 200% faster than the serial code, does it run in half the time of the serial version or one-third of the time? Is 105% speedup almost the same time as the serial execution or more than twice as fast? Is the baseline serial time 0% speedup or 100% speedup? On the other hand, if the parallel application were reported to have a speedup of 2X, it is clear that it took half the time (i.e., the parallel version could have executed twice in the same time it took the serial code to execute once).

In very rare circumstances, the speedup of an application exceeds the number of cores. This phenomenon is known as super-linear speedup. The typical cause for super-linear speedup is that decomposition of the fixed-size data set has become small enough per core to fit into local cache. When running in serial, the data had to stream through cache, and the processor was made to wait while cache lines were fetched. If the data was large enough to evict some previously used cache lines, any subsequent reuse of those early cache lines would cause the processor to wait once more for cache lines. When the data is divided into chunks that all fit into the cache on a core, there is no waiting for reused cache lines once they have all been placed in the cache. Thus, the use of multiple cores can eliminate some of the overhead associated with the serial code executing on a single core. Data sets that are too small—smaller than a typical data set size—can give a false sense of performance improvement.

#### **Usage Guidelines**

Other parallel execution models have been proposed that attempt to make reasonable assumptions for the discrepancies in the simple model of Amdahl's Law.

Still, for its simplicity and the understanding by the user that this is a theoretical upper bound, which is very unlikely to be achieved or surpassed, Amdahl's Law is a simple and valuable indication of the potential for speedup in a serial application.

### **Additional Resources**

Intel® Software Network Parallel Programming Community

John L. Gustafson. "Reevaluating Amdahl's Law." *Communications of the ACM,* Vol. 31, pp. 532-533, 1988.

Michael J. Quinn. Parallel Programming in C with MPI and OpenMP. McGraw-Hill, 2004.

# Loop Modifications to Enhance Data-Parallel Performance

#### Abstract

In data-parallel applications, the same independent operation is performed repeatedly on different data. Loops are usually the most compute-intensive segments of data parallel applications, so loop optimizations directly impact performance. When confronted with nested loops, the granularity of the computations that are assigned to threads will directly affect performance. Loop transformations such as splitting (loop fission) and merging (loop fusion) nested loops can make parallelization easier and more productive.

#### **Background**

Loop optimizations offer a good opportunity to improve the performance of data-parallel applications. These optimizations, such as loop fusion, loop interchange, and loop unrolling, are usually targeted at improving granularity, load balance, and data locality, while minimizing synchronization and other parallel overheads. As a rule of thumb, loops with high iteration counts are typically the best candidates for parallelization, especially when using a relatively small number of threads. A higher iteration count enables better load balance due to the availability of a larger number of tasks that can be distributed among the threads. Still, the amount of work to be done per iteration should also be considered. Unless stated otherwise, the discussion in this section assumes that the amount of computation within each iteration of a loop is (roughly) equal to every other iteration in the same loop.

Consider the scenario of a loop using the OpenMP\* for worksharing construct shown in the example code below. In this case, the low iteration count leads to a load imbalance when the loop iterations are distributed over four threads. If a single iteration takes only a few microseconds, this imbalance may not cause a significant impact. However, if each iteration takes an hour, three of the threads remain idle for 60 minutes while the fourth completes. Contrast this to the same loop with 1003 one-hour iterations and four threads. In this case, a single hour of idle time after ten days of execution is insignificant.

```

#pragma omp for

for (i = 0; i < 13; i++)

{...}</pre>

```

#### Advice

For multiple nested loops, choose the outermost loop that is safe to parallelize. This approach generally gives the coarsest granularity. Ensure that work can be evenly distributed to each thread. If this is not possible because the outermost loop has a low iteration count, an inner loop with a large iteration count may be a better candidate for threading. For example, consider the following code with four nested loops:

```

void processQuadArray (int imx, int jmx, int kmx,

double**** w, double**** ws)

{

for (int nv = 0; nv < 5; nv++)

for (int k = 0; k < kmx; k++)

for (int j = 0; j < jmx; j++)</pre>

```

```

for (int i = 0; i < imx; i++)

ws[nv][k][j][i] = Process(w[nv][k][j][i]);

}</pre>

```

With any number other than five threads, parallelizing the outer loop will result in load imbalance and idle threads. The inefficiency would be especially severe if the array dimensions imx, jmx, and kmx are very large. Parallelizing one of the inner loops is a better option in this case.

Avoid the implicit barrier at the end of worksharing constructs when it is safe to do so. All OpenMP worksharing constructs (for, sections, single) have an implicit barrier at the end of the structured block. All threads must rendezvous at this barrier before execution can proceed. Sometimes these barriers are unnecessary and negatively impact performance. Use the OpenMP nowait clause to disable this barrier, as in the following example:

Since the computations in the innermost loop are all independent, there is no reason for threads to wait at the implicit barrier before going on to the next k iteration. If the amount of work per iteration is unequal, the <code>nowait</code> clause allows threads to proceed with useful work rather than sit idle at the implicit barrier.

If a loop has a loop-carried dependence that prevents the loop from being executed in parallel, it may be possible to break up the body of the loop into separate loops than can be executed in parallel. Such division of a loop body into two or more loops is known as "loop fission". In the following example, loop fission is performed on a loop with a dependence to create new loops that can execute in parallel:

```

float *a, *b;

int i;

for (i = 1; i < N; i++) {

if (b[i] > 0.0)

a[i] = 2.0 * b[i];

else

a[i] = 2.0 * fabs(b[i]);

b[i] = a[i-1];

}

```

The assignment of elements within the a array are all independent, regardless of the sign of the corresponding elements of b. Each assignment of an element in b is independent of any other

assignment, but depends on the completion of the assignment of the required element of a. Thus, as written, the loop above cannot be parallelized.

By splitting the loop into the two independent operations, both of those operations can be executed in parallel. For example, the Intel® Threading Building Blocks (Intel® TBB) parallel for algorithm can be used on each of the resulting loops as seen here:

```

float *a, *b;

parallel_for (1, N, 1,

[&](int i) {

if (b[i] > 0.0)

a[i] = 2.0 * b[i];

else

a[i] = 2.0 * fabs(b[i]);

});

parallel_for (1, N, 1,

[&](int i) {

b[i] = a[i-1];

});

```

The return of the first parallel\_for call before execution of the second ensures that all the updates to the a array have completed before the updates on the b array are started.

Another use of loop fission is to increase data locality. Consider the following sieve-like code:

```

for (i = 0; i < list_len; i++)

for (j = prime[i]; j < N; j += prime[i])

marked[j] = 1;</pre>

```

The outer loop selects the starting index and step of the inner loop from the prime array. The inner loop then runs through the length of the marked array depositing a 1' value into the chosen elements. If the marked array is large enough, the execution of the inner loop can evict cache lines from the early elements of marked that will be needed on the subsequent iteration of the outer loop. This behavior will lead to a poor cache hit rate in both serial and parallel versions of the loop.

Through loop fission, the iterations of the inner loop can be broken into chunks that will better fit into cache and reuse the cache lines once they have been brought in. To accomplish the fission in this case, another loop is added to control the range executed over by the innermost loop:

```

for (k = 0; k < N; k += CHUNK_SIZE)

for (i = 0; i < list_len; i++) {

start = f(prime[i], k);

end = g(prime[i], k);

for (j = start; j < end; j += prime[i])

marked[j] = 1;

}</pre>

```

For each iteration of the outermost loop in the above code, the full set of iterations of the i-loop will execute. From the selected element of the prime array, the start and end indices within the chunk of the marked array (controlled by the outer loop) must be found. These computations have been encapsulated within the f() and g() routines. Thus, the same chunk of marked will

be processed before the next one is processed. And, since the processing of each chunk is independent of any other, the iteration of the outer loop can be made to run in parallel.

Merging nested loops to increase the iteration count is another optimization that may aid effective parallelization of loop iterations. For example, consider the code on the left with two nested loops having iteration counts of 23 and 1000, respectively. Since 23 is prime, there is no way to evenly divide the outer loop iterations; also, 1000 iteration may not be enough work to sufficiently minimize the overhead of threading only the inner loop. On the other hand, the loops can be fused into a single loop with 23,000 iterations (as seen on the right), which could alleviate the problems with parallelizing the original code.

```

#define N 23

#define M 1000

...

for (k = 0; k < N; k++)

for (j = 0; j < M; j++)

wn[k][j] = Work(w[k][j], k,

j);

#define N 23

#define M 1000

...

for (kj = 0; kj < N*M; kj++) {

k = kj / M;

j = kj % M;

wn [k][j] = Work(w[k][j], k,

j);

}</pre>

```

However, if the iteration variables are each used within the loop body (e.g., to index arrays), the new loop counter must be translated back into the corresponding component values, which creates additional overhead that the original algorithm did not have.

Fuse (or merge) loops with similar indices to improve granularity and data locality and to minimize overhead when parallelizing. The first two loops in the left-hand example code can be easily merged:

Merging these loops increases the amount of work per iteration (i.e., granularity) and reduces loop overhead. The third loop is not easily merged because its iteration count is different. More important, however, a data dependence exists between the third loop and the previous two loops.

Use the OpenMP if clause to choose serial or parallel execution based on runtime information. Sometimes the number of iterations in a loop cannot be determined until runtime. If there is a negative performance impact for executing an OpenMP parallel region with multiple threads (e.g., a small number of iterations), specifying a minimum threshold will help maintain performance, as in the following example:

```

#pragma omp parallel for if(N >= threshold)

for (i = 0; i < N; i++) { ... }

```

For this example code, the loop is only executed in parallel if the number of iterations exceeds the threshold specified by the programmer.

Since there is no equivalent in Intel TBB, an explicit conditional test could be done to determine if a parallel or serial execution of code should be done. Alternately, a parallel algorithm could be called and the Intel TBB task scheduler could be given free rein to determine that a single thread should be used for low enough values of  $\mathbb N$ . There would be some overhead required for this last option.

#### **Additional Resources**

Intel® Software Network Parallel Programming Community

OpenMP\* Specifications

Intel® Threading Building Blocks

Intel Threading Building Blocks for Open Source

James Reinders, *Intel Threading Building Blocks: Outfitting C++ for Multi-core Processor Parallelism*. O'Reilly Media, Inc. Sebastopol, CA, 2007.

# Granularity and Parallel Performance

#### Abstract

One key to attaining good parallel performance is choosing the right granularity for the application. Granularity is the amount of real work in the parallel task. If granularity is too fine, then performance can suffer from communication overhead. If granularity is too coarse, then performance can suffer from load imbalance. The goal is to determine the right granularity (usually larger is better) for parallel tasks, while avoiding load imbalance and communication overhead to achieve the best performance.

#### **Background**

The size of work in a single parallel task (granularity) of a multithreaded application greatly affects its parallel performance. When decomposing an application for multithreading, one approach is to logically *partition* the problem into as many parallel tasks as possible. Within the parallel tasks, next determine the necessary *communication* in terms of shared data and execution order. Since partitioning tasks, assigning the tasks to threads, and communicating (sharing) data between tasks are not free operations, one often needs to *agglomerate*, or combine partitions, to overcome these overheads and achieve the most efficient implementation. The agglomeration step is the process of determining the best granularity for parallel tasks.

The granularity is often related to how balanced the work load is between threads. While it is easier to balance the workload of a large number of smaller tasks, this may cause too much parallel overhead in the form of communication, synchronization, etc. Therefore, one can reduce parallel overhead by increasing the granularity (amount of work) within each task by combining smaller tasks into a single task. Tools such as the Intel® Parallel Amplifier can help identify the right granularity for an application.

The following examples demonstrate how to improve the performance of a parallel program by decreasing the communication overhead and finding the right granularity for the threads. The example used throughout this article is a prime-number counting algorithm that uses a simple brute force test of all dividing each potential prime by all possible factors until a divisor is found or the number is shown to be a prime. Because positive odd numbers can be computed by either (4k+1) or (4k+3), for  $k \ge 0$ , the code will also keep a count of the prime numbers that fall into each form. The examples will count all of the prime numbers between 3 and 1 million.

The first variation of the code shows a parallel version using OpenMP\*:

```

numPrimes++;

if (i%4 == 1) numP41++;  // 4k+1 primes

if (i%4 == 3) numP43++;  // 4k-1 primes

}

}

}

```

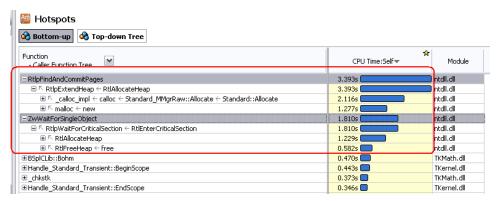

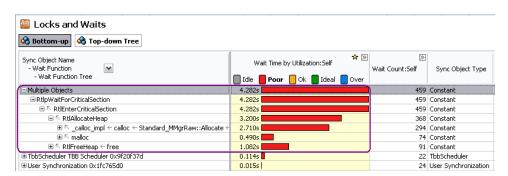

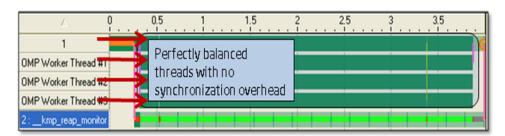

This code has both high communication overhead (in the form of synchronization), and an individual task size that is too small for the threads. Inside the loop, there is a critical region that is used to provide a safe mechanism for incrementing the counting variables. The critical region adds synchronization and lock overhead to the parallel loop as shown by the Intel Parallel Amplifier display in Figure 1.

| Locks and Waits □ Locks and Waits □ Intel® Parallel Amp □ Top-down Tree |                               |                                                          |                                                                             |                               |  |  |

|-------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------|--|--|

| Wait Time by Utilization:Self ☆ ☑  Idle Poor Ok Ideal Over              | Wait<br>Count:Self            | Sync Object Type                                         | Creation Function                                                           | Creation<br>Module            |  |  |

| 2.683s                                                                  | 78495                         | OMP Critical                                             | L_main_57_pa                                                                | PrimeOpenMP.exe               |  |  |

| 0.000s                                                                  | 2                             | Stream                                                   | Lmain_57pa                                                                  | PrimeOpenMP.exe               |  |  |

| 0.000s                                                                  | 1                             | None                                                     | Lmain_57pa                                                                  | PrimeOpenMP.exe               |  |  |

| 0.000s                                                                  | 3                             | Thread                                                   | main                                                                        | PrimeOpenMP.exe               |  |  |

| 0.000s                                                                  | 1                             | Manual Reset Ev                                          | main                                                                        | PrimeOpenMP.exe               |  |  |

| 0.000s l                                                                | 1                             | Thread                                                   | main                                                                        | PrimeOpenMP.exe               |  |  |

|                                                                         | Wait Time by Utilization:Self | Wait Time by Utilization:Self   Wait Count:Self     Idle | Wait Time by Utilization:Self   Wait Count:Self   Sync Object Type     Idle | Wait Time by Utilization:Self |  |  |

**Figure 1.** Locks and Waits analysis results demonstrating that the OpenMP\* critical region is cause of synchronization overhead.

The incrementing of counter variables based on values within a large dataset is a common expression that is referred to as a reduction. The lock and synchronization overhead can be removed by eliminating the critical region and adding an OpenMP reduction clause:

```

#pragma omp parallel

int j, limit, prime;

#pragma for schedule(dynamic, 1) \

reduction(+:numPrimes, numP41, numP43)

for(i = 3; i <= 1000000; i += 2) {

limit = (int) sqrt((float)i) + 1;

prime = 1; // assume number is prime

j = 3;

while (prime && (j <= limit))

if (i\%j == 0) prime = 0;

j += 2;

}

if (prime)

numPrimes++;

if (i%4 == 1) numP41++; // 4k+1 primes

if (i%4 == 3) numP43++; // 4k-1 primes

```

```

}

```

Depending on how many iterations are executed for a loop, removal of a critical region within the body of the loop can improve the execution speed by orders of magnitude. However, the code above may still have some parallel overhead. This is caused by the work size for each task being too small. The schedule (dynamic, 1) clause specifies that the scheduler distribute one iteration (or chunk) at a time dynamically to each thread. Each worker thread processes one iteration and then returns to the scheduler, and synchronizes to get another iteration. By increasing the chunk size, we increase the work size for each task that is assigned to a thread and therefore reduce the number of times each thread must synchronize with the scheduler.

While this approach can improve performance, one must bear in mind (as mentioned above) that increasing the granularity too much can cause load imbalance. For example, consider increasing the chunk size to 10000, as in the code below:

```

#pragma omp parallel

int j, limit, prime;

#pragma for schedule(dynamic, 100000) \

reduction(+:numPrimes, numP41, numP43)

for(i = 3; i \le 1000000; i += 2)

limit = (int) sqrt((float)i) + 1;

prime = 1; // assume number is prime

j = 3;

while (prime && (j <= limit))

if (i\%j == 0) prime = 0;

j += 2;

if (prime)

numPrimes++;

if (i%4 == 1) numP41++; // 4k+1 primes

if (i%4 == 3) numP43++; // 4k-1 primes

}

}

}

```

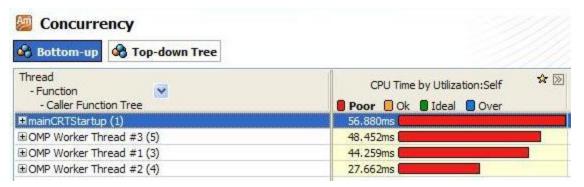

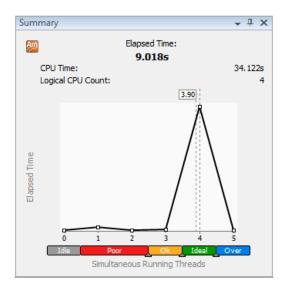

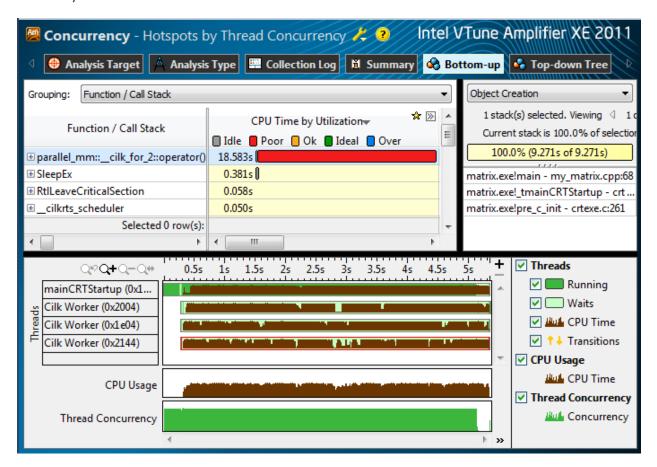

Analysis of the execution of this code within Parallel Amplifier shows an imbalance in the amount of computation done by the four threads used, as shown in Figure 2. The key point for this computation example is that each chunk has a different amount of work and there are too few chunks to be assigned as tasks (ten chunks for four threads), which causes the load imbalance. As the value of the potential primes increases (from the for loop), more iterations are required to test all possible factors for prime numbers (in the while loop). Thus, the total work for each chunk will require more iteration of the while loop than the previous chunks.

**Figure 2.** Concurrency analysis results demonstrating the imbalance of execution time used by each thread.

A more appropriate work size (100) should be used to select the right granularity for the program. Also, since the difference in the amount of work between consecutive tasks will be less severe than the previous chunk size, a further elimination of parallel overhead can be accomplished by using the static schedule rather than dynamic. The code below shows the change in the schedule clause that will virtually the overhead from this code segment and produce the fastest overall parallel performance.

```

#pragma omp parallel

int j, limit, prime;

#pragma for schedule(static, 100) \

reduction(+:numPrimes, numP41, numP43)

for(i = 3; i \le 1000000; i += 2)

limit = (int) sqrt((float)i) + 1;

prime = 1; // assume number is prime

j = 3;

while (prime && (j <= limit))

if (i%j == 0) prime = 0;

j += 2;

if (prime)

numPrimes++;

if (i%4 == 1) numP41++; // 4k+1 primes

if (i%4 == 3) numP43++; // 4k-1 primes

}

```

#### **Advice**

Parallel performance of multithreaded code depends on granularity: how work is divided among threads and how communication is accomplished between those threads. Following are some guidelines for improving performance by adjusting granularity:

Know your application

- Understand how much work is being done in various parts of the application that will be executed in parallel.

- Understand the communication requirements of the application. Synchronization is a common form of communication, but also consider the overhead of message passing and data sharing across memory hierarchies (cache, main memory, etc.).

- Know your platform and threading model

- Know the costs of launching parallel execution and synchronization with the threading model on the target platform.

- Make sure that the application's work per parallel task is much larger than the overheads of threading.

- Use the least amount of synchronization possible and use the lowest-cost synchronization possible.

- Use a partitioner object in Intel® Threading Building Blocks parallel algorithms to allow the task scheduler to choose a good granularity of work per task and load balance on execution threads.

- Know your tools

- o In Intel Parallel Amplifier "Locks and Waits" analysis, look for significant lock, synchronization, and parallel overheads as a sign of too much communication.

- In Intel Parallel Amplifier "Concurrency" analysis, look for load imbalance as a sign of the granularity being too large or tasks needing a better distribution to threads.

#### **Usage Guidelines**

While the examples above make reference to OpenMP frequently, all of the advice and principles described apply to other threading models, such as Windows threads and POSIX\* threads. All threading models have overhead associated with their various functions, such as launching parallel execution, locks, critical regions, message passing, etc. The advice here about reducing communication and increasing work size per thread without increasing load imbalance applies to all threading models. However, the differing costs of the differing models may dictate different choices of granularity.

#### **Additional Resources**

Intel® Software Network Parallel Programming Community

Clay Breshears, *The Art of Concurrency*, O'Reilly Media, Inc., 2009.

Barbara Chapman, Gabriele Jost, and Ruud van der Post, *Using OpenMP: Portable Shared Memory Parallel Programming*, The MIT Press, 2007.

Intel® Threading Building Blocks

Intel Threading Building Blocks for Open Source

James Reinders, *Intel Threading Building Blocks: Outfitting C++ for Multi-core Processor Parallelism.* O'Reilly Media, Inc. Sebastopol, CA, 2007.

Ding-Kai Chen, et al, "The Impact of Synchronization and Granularity on Parallel Systems", Proceedings of the 17th Annual International Symposium on Computer Architecture 1990, Seattle, Washington, USA.

#### Load Balance and Parallel Performance

#### Abstract

Load balancing an application workload among threads is critical to performance. The key objective for load balancing is to minimize idle time on threads. Sharing the workload equally across all threads with minimal work sharing overheads results in fewer cycles wasted with idle threads not advancing the computation, and thereby leads to improved performance. However, achieving perfect load balance is non-trivial, and it depends on the parallelism within the application, workload, the number of threads, load balancing policy, and the threading implementation.

#### Background

An idle core during computation is a wasted resource, and when effective parallel execution could be running on that core, it increases the overall execution time of a threaded application. This idleness can result from many different causes, such as fetching from memory or I/O. While it may not be possible to completely avoid cores being idle at times, there are measures that programmers can apply to reduce idle time, such as overlapped I/O, memory prefetching, and reordering data access patterns for better cache utilization.

Similarly, idle threads are wasted resources in multithreaded executions. An unequal amount of work being assigned to threads results in a condition known as a "load imbalance." The greater the imbalance, the more threads will remain idle and the greater the time needed to complete the computation. The more equitable the distribution of computational tasks to available threads, the lower the overall execution time will be.

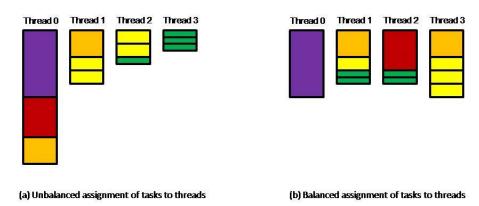

As an example, consider a set of twelve independent tasks with the following set of execution times:  $\{10, 6, 4, 4, 2, 2, 2, 2, 1, 1, 1, 1\}$ . Assuming that four threads are available for computing this set of tasks, a simple method of task assignment would be to schedule each thread with three total tasks distributed in order. Thus, Thread 0 would be assigned work totaling 20 time units (10+6+4), Thread 1 would require 8 time units (4+2+2), Thread 2 would require 5 time units (2+2+1), and Thread 3 would be able to execute the three tasks assigned in only 3 time units (1+1+1). Figure 1(a) illustrates this distribution of work and shows that the overall execution time for these twelve tasks would be 20 time units (time runs from top to bottom).

Figure 1. Examples of task distribution among four threads.

A better distribution of work would have been Thread 0: {10}, Thread 1: {4, 2, 1, 1}, Thread 2: {6, 1, 1}, and Thread 3: {4, 2, 2, 2}, as shown in Figure 1(b). This schedule would take only 10 time units to complete and with only have two of the four threads idle for 2 time units each.

#### Advice

For the case when all tasks are the same length, a simple static division of tasks among available threads—dividing the total number of tasks into (nearly) equal-sized groups assigned to each thread—is an easy and equitable solution. In the general case, however, even when all task lengths are known in advance, finding an optimal, balanced assignment of tasks to threads is an intractable problem. When the lengths of individual tasks are not the same, a better solution may be a more dynamic division of tasks to the assigned threads.

The OpenMP\* iterative worksharing construct typically defaults to static scheduling of iterations onto threads (if not, this can scheduling can be specified). When the workload varies among the iterations and the pattern is unpredictable, a dynamic scheduling of iterations to threads can better balance the load. Two scheduling alternatives, dynamic and guided, are specified through the schedule clause. Under dynamic scheduling, chunks of iterations are assigned to threads; when the assignment has been completed, threads request a new chunk of iterations. The optional chunk argument of the schedule clause denotes the fixed size of iteration chunks for dynamic scheduling.

```

#pragma omp parallel for schedule(dynamic, 5)

for (i = 0; i < n; i++)

{

unknown_amount_of_work(i);

}</pre>

```

Guided scheduling initially assigns initially large chunks of iterations to threads; the number of iterations given to requesting threads is reduced in size as the set of unassigned iterations decreases. Because of the pattern of assignment, guided scheduling tends to require less overhead than dynamic scheduling. The optional chunk argument of the schedule clause denotes the minimum number of iterations in a chunk to be assigned under guided scheduling.

```

#pragma omp parallel for schedule(guided, 8)

for (i = 0; i < n; i++)

{

uneven_amount_of_work(i);

}</pre>

```

A special case is when the workload between iterations is monotonically increasing (or decreasing). For example, the number of elements per row in a lower triangular matrix increases in a regular pattern. For such cases, setting a relatively low chunk size (to create a large number of chunks/tasks) with static scheduling may provide an adequate amount of load balance without the overheads needed for dynamic or guided scheduling.

```

#pragma omp parallel for schedule(static, 4)

for (i = 0; i < n; i++)

{

process_lower_triangular_row(i);

}</pre>

```

When the choice of schedule is not apparent, use of the runtime schedule allows the alteration of chunk size and schedule type as desired, without requiring recompilation of the program.

When using the <code>parallel\_for</code> algorithm from Intel® Threading Building Blocks (Intel® TBB), the scheduler divides the iteration space into small tasks that are assigned to threads. If the computation time of some iterations proves to take longer than other iterations, the Intel TBB scheduler is able to dynamically "steal" tasks from threads in order to achieve a better work load balance among threads.

Explicit threading models (e.g., Windows\* threads, Pthreads\*, and Java\* threads) do not have any means to automatically schedule a set of independent tasks to threads. When needed, such capability must be programmed into the application. Static scheduling of tasks is a straightforward exercise. For dynamic scheduling, two related methods are easily implemented: Producer/Consumer and Boss/Worker. In the former, one thread (Producer) places tasks into a shared queue structure while the Consumer threads remove tasks to be processed, as needed. While not strictly necessary, the Producer/Consumer model is often used when there is some preprocessing to be done before tasks are made available to Consumer threads.

Under the Boss/Worker model, Worker threads rendezvous with the Boss thread whenever more work is needed, to receive assignments directly. In situations where the delineation of a task is very simple, such as a range of indices to an array of data for processing, a global counter with proper synchronization can be used in place of a separate Boss thread. That is, Worker threads access the current value and adjust (likely increment) the counter for the next thread requesting additional work.

Whatever task scheduling model is used, consideration must be given to using the correct number and mix of threads to ensure that threads tasked to perform the required computations are not left idle. For example, if Consumer threads stand idle at times, a reduction in the number of Consumers or an additional Producer thread may be needed. The appropriate solution will depend on algorithmic considerations as well as the number and length of tasks to be assigned.

#### **Usage Guidelines**

Any dynamic task scheduling method will entail some overhead as a result of parceling out tasks. Bundling small independent tasks together as a single unit of assignable work can reduce this overhead; correspondingly, if using OpenMP schedule clauses, set a non-default chunk size that will be the minimum number of iterations within a task. The best choice for how much computation constitutes a task will be based on the computation to be done as well as the number of threads and other resources available at execution time.

#### Additional Resources

Intel® Software Network Parallel Programming Community

Clay Breshears, *The Art of Concurrency*, O'Reilly Media, Inc., 2009.

Barbara Chapman, Gabriele Jost, and Ruud van der Post, *Using OpenMP: Portable Shared Memory Parallel Programming*, The MIT Press, 2007.

Intel® Threading Building Blocks

Intel Threading Building Blocks for Open Source

James Reinders, *Intel Threading Building Blocks: Outfitting C++ for Multi-core Processor Parallelism*, O'Reilly Media, Inc. Sebastopol, CA, 2007.

M. Ben-Ari, *Principles of Concurrent and Distributed Programming*, Second Edition, Addison-Wesley, 2006.

# Expose Parallelism by Avoiding or Removing Artificial Dependencies

#### **Abstract**

Many applications and algorithms contain serial optimizations that inadvertently introduce data dependencies and inhibit parallelism. One can often remove such dependences through simple transforms, or even avoid them altogether through techniques such as domain decomposition or blocking.

#### **Background**

While multithreading for parallelism is an important source of performance, it is equally important to ensure that each thread runs efficiently. While optimizing compilers do the bulk of this work, it is not uncommon for programmers to make source code changes that improve performance by exploiting data reuse and selecting instructions that favor machine strengths. Unfortunately, the same techniques that improve serial performance can inadvertently introduce data dependencies that make it difficult to achieve additional performance through multithreading.

One example is the re-use of intermediate results to avoid duplicate computations. As an example, softening an image through blurring can be achieved by replacing each image pixel by a weighted average of the pixels in its neighborhood, itself included. The following pseudo-code describes a 3x3 blurring stencil:

```

for each pixel in (imageIn)

sum = value of pixel

// compute the average of 9 pixels from imageIn

for each neighbor of (pixel)

sum += value of neighbor

// store the resulting value in imageOut

pixelOut = sum / 9

```

The fact that each pixel value feeds into multiple calculations allows one to exploit data reuse for performance. In the following pseudo-code, intermediate results are computed and used three times, resulting in better serial performance:

```

subroutine BlurLine (lineIn, lineOut)

for each pixel j in (lineIn)

// compute the average of 3 pixels from line

// and store the resulting value in lineout

pixelOut = (pixel j-1 + pixel j + pixel j+1) / 3

declare lineCache[3]

lineCache[0] = 0

BlurLine (line 1 of imageIn, lineCache[1])

for each line i in (imageIn)

BlurLine (line i+1 of imageIn, lineCache[i mod 3])

lineSums = lineCache[0] + lineCache[1] + lineCache[2]

lineOut = lineSums / 3

```

This optimization introduces a dependence between the computations of neighboring lines of the output image. If one attempts to compute the iterations of this loop in parallel, the dependencies will cause incorrect results.

Another common example is pointer offsets inside a loop:

```

ptr = &someArray[0]

for (i = 0; i < N; i++)

{

Compute (ptr);

ptr++;

}</pre>

```

By incrementing ptr, the code potentially exploits the fast operation of a register increment and avoids the arithmetic of computing someArray[i] for each iteration. While each call to compute may be independent of the others, the pointer becomes an explicit dependence; its value in each iteration depends on that in the previous iteration.

Finally, there are often situations where the algorithms invite parallelism but the data structures have been designed to a different purpose that unintentionally hinder parallelism. Sparse matrix algorithms are one such example. Because most matrix elements are zero, the usual matrix representation is often replaced with a "packed" form, consisting of element values and relative offsets, used to skip zero-valued entries.

This article presents strategies to effectively introduce parallelism in these challenging situations.

#### Advice

Naturally, it's best to find ways to exploit parallelism without having to remove existing optimizations or make extensive source code changes. Before removing any serial optimization to expose parallelism, consider whether the optimization can be preserved by applying the existing kernel to a subset of the overall problem. Normally, if the original algorithm contains parallelism, it is also possible to define subsets as independent units and compute them in parallel.

To efficiently thread the blurring operation, consider subdividing the image into sub-images, or blocks, of fixed size. The blurring algorithm allows the blocks of data to be computed independently. The following pseudo-code illustrates the use of image blocking:

```

// One time operation:

// Decompose the image into non-overlapping blocks.

blockList = Decompose (image, xRes, yRes)

foreach (block in blockList)

{

BlurBlock (block, imageIn, imageOut)

}

```

The existing code to blur the entire image can be reused in the implementation of BlurBlock. Using OpenMP or explicit threads to operate on multiple blocks in parallel yields the benefits of multithreading and retains the original optimized kernel.

In other cases, the benefit of the existing serial optimization is small compared to the overall cost of each iteration, making blocking unnecessary. This is often the case when the iterations are sufficiently coarse-grained to expect a speedup from parallelization. The pointer increment example is one such instance. The induction variables can be easily replaced with explicit indexing, removing the dependence and allowing simple parallelization of the loop.

```

ptr = &someArray[0]

```

```

for (i = 0; i < N; i++)

{

Compute (ptr[i]);

}</pre>

```

Note that the original optimization, though small, is not necessarily lost. Compilers often optimize index calculations aggressively by utilizing increment or other fast operations, enabling the benefits of both serial and parallel performance.

Other situations, such as code involving packed sparse matrices, can be more challenging to thread. Normally, it is not practical to unpack data structures but it is often possible to subdivide the matrices into blocks, storing pointers to the beginning of each block. When these matrices are paired with appropriate block-based algorithms, the benefits of a packed representation and parallelism can be simultaneously realized.

The blocking techniques described above are a case of a more general technique called "domain decomposition." After decomposition, each thread works independently on one or more domains. In some situations, the nature of the algorithms and data dictate that the work per domain will be nearly constant. In other situations, the amount of work may vary from domain to domain. In these cases, if the number of domains equals the number of threads, parallel performance can be limited by load imbalance. In general, it is best to ensure that the number of domains is reasonably large compared to the number of threads. This will allow techniques such as dynamic scheduling to balance the load across threads.

#### **Usage Guidelines**

Some serial optimizations deliver large performance gains. Consider the number of processors being targeted to ensure that speedups from parallelism will outweigh the performance loss associated with optimizations that are removed.

Introducing blocking algorithms can sometimes hinder the compiler's ability to distinguish aliased from unaliased data. If, after blocking, the compiler can no longer determine that data is unaliased, performance may suffer. Consider using the restrict keyword to explicitly prohibit aliasing. Enabling inter-procedural optimizations also helps the compiler detect unaliased data.

#### **Additional Resources**

Intel® Software Network Parallel Programming Community

OpenMP\* Specifications

# Using Tasks Instead of Threads

#### Abstract

Tasks are a light-weight alternative to threads that provide faster startup and shutdown times, better load balancing, an efficient use of available resources, and a higher level of abstraction. Three programming models that include task based programming are Intel® Threading Building Blocks (Intel® TBB) and OpenMP\*. This article provides a brief overview of task-based programming and some important guidelines for deciding when to use threads and when to use tasks.

#### **Background**

Programming directly with a native threading package is often a poor choice for multithreaded programming. Threads created with these packages are logical threads that are mapped by the operating system onto the physical threads of the hardware. Creating too few logical threads will undersubscribe the system, wasting some of the available hardware resources. Creating too many logical threads will oversubscribe the system, causing the operating system to incur considerable overhead as it must time-slice access to the hardware resources. By using native threads directly, the developer becomes responsible for matching the parallelism available in the application with the resources available in the hardware.

One common way to perform this difficult balancing act is to create a pool of threads that are used across the lifetime of an application. Typically, one logical thread is created per physical thread. The application then dynamically schedules computations on to threads in the thread pool. Using a thread pool not only helps to match parallelism to hardware resources but also avoids the overheads incurred by repeated thread creation and destruction.

Some parallel programming models, such as Intel TBB and the OpenMP API provide developers with the benefits of thread pools without the burden of explicitly managing the pools. Using these models, developers express the logical parallelism in their applications with tasks, and the runtime library schedules these tasks on to its internal pool of worker threads. Using tasks, developers can focus on the logical parallelism in their application without worrying about managing the parallelism. Also, since tasks are much lighter weight than threads, it is possible to express parallelism at a much finer granularity.

A simple example of using tasks is shown below. The function fibted calculates the  $n^{th}$  Fibonacci number using a TBB task\_group. At each call where n >= 10, a task group is created and two tasks are run. In this example, a lambda expression (a feature in the proposed C++0x standard) that describes each task is passed to the function run. These calls spawn the tasks, which makes them available for threads in the thread pool to execute. The subsequent call to the function wait blocks until all of the tasks in the task group have run to completion.

```

int fibTBB(int n) {

if( n<10 ) {

return fibSerial(n);

} else {

int x, y;

tbb::task_group g;

g.run([&]{x=Fib(n-1);}); // spawn a task

g.run([&]{y=Fib(n-2);}); // spawn another task

g.wait(); // wait for both tasks to complete

return x+y;</pre>

```

```

}

```

The routine fibSerial is presumed to be a serial variant. Though tasks enable finer grain parallelism than tasks, they still have significant overhead compared to a subroutine call. Therefore, it generally pays to solve small subproblems serially.

Other libraries that support tasks include the OpenMP API. Unlike Intel TBB, both of these models use compiler support, which makes their interfaces simpler but less portable. For example, the same Fibonacci example shown above using TBB tasks is implemented as fibOpenMP below using OpenMP tasks. Because OpenMP requires compiler support, simpler pragmas can be used to denote tasks. However, only compilers that support the OpenMP API will understand these pragmas.

```

int fibOpenMP( int n ) {

int i, j;

if( n < 10 ) {

return fibSerial(n);

} else {

// spawn a task

#pragma omp task shared( i ), untied

i = fib(n - 1);

// spawn another task

#pragma omp task shared( j ), untied

j = fib(n - 2);

// wait for both tasks to complete

#pragma omp taskwait

return i + j;

}

}

```

Intel TBB and the OpenMP API manage task scheduling through work stealing. In work stealing, each thread in the thread pool maintains a local task pool that is organized as a deque (double-ended queue). A thread uses its own task pool like a stack, pushing new tasks that it spawns onto the top of this stack. When a thread finishes executing a task, it first tries to pop a task from the top of its local stack. The task on the top of the stack is the newest and therefore most likely to access data that is hot in its data cache. If there are no tasks in its local task pool, however, it attempts to steal work from another thread (the victim). When stealing, a thread uses the victim's deque like a queue so that it steals the oldest task from the victim's deque. For recursive algorithms, these older tasks are nodes that are high in the task tree and therefore are large chunks of work, often work that is not hot in the victim's data cache. Therefore, work stealing is an effective mechanism for balancing load while maintaining cache locality.

The thread pool and the work-stealing scheduler that distributes work across the threads are hidden from developers when a tasking library is used. Therefore, tasks provide a high-level abstraction that lets users think about the logical parallelism in their application without worrying about managing the parallelism. The load balancing provided by work-stealing and the low creation and destruction costs for tasks make task-based parallelism an effective solution for most applications.

#### **Usage Guidelines**

While using tasks is usually the best approach to adding threading for performance, there are cases when using tasks is not appropriate. The task schedulers used by Intel TBB and the

OpenMP API are non-preemptive. Tasks are therefore intended for high-performance algorithms that are non-blocking. They still work well if the tasks rarely block. However, if tasks block frequently, there is a performance loss because while a task is blocked, the thread it has been assigned to cannot work on any other tasks. Blocking typically occurs while waiting for I/O or mutexes for long periods. If threads hold mutexes for long periods, the code is not likely to perform well, regardless of how many threads it has. For blocking tasks, it is best to use threads rather than tasks.

Even in cases when using tasks is best, sometimes it's not necessary to implement the tasking pattern from scratch. The Intel TBB library provides not only a task interface but also high-level algorithms that implement some of the most common task patterns, such as parallel\_invoke, parallel\_for, parallel\_reduce and pipeline. The OpenMP API also offers parallel loops. Since these patterns have been tuned and tested, it's best to use these high-level algorithms whenever possible.

The example below shows a simple serial loop and a parallel version of the loop that uses the tbb::parallel for algorithm:

```

// serial loop

for (int i = 0; i < 10000; ++i)

a[i] = f(i) + g(i);

// parallel loop

tbb::parallel for( 0, 10000, [&](int i) { a[i] = f(i) + g(i); } );</pre>

```

In the example above, the TBB <code>parallel\_for</code> creates tasks that apply the loop body, in this case <code>a[i] = f(i) + g(i)</code>, to each of the elements in the range [0,10000). The & in the lambda expression indicates that variable a should be captured by reference. When using a <code>parallel\_for</code>, the TBB runtime library chooses an appropriate number of iterations to group together in a single task to minimize overheads while providing ample tasks for load balancing.

#### **Additional Resources**

Intel® Software Network Parallel Programming Community

Intel® Threading Building Blocks

Intel Threading Building Blocks for Open Source

James Reinders, *Intel Threading Building Blocks: Outfitting C++ for Multi-core Processor Parallelism.* O'Reilly Media, Inc. Sebastopol, CA, 2007.

OpenMP\* Specifications

# Exploiting Data Parallelism in Ordered Data Streams

#### Abstract

Many compute-intensive applications involve complex transformations of ordered input data to ordered output data. Examples include sound and video transcoding, lossless data compression, and seismic data processing. While the algorithms employed in these transformations are often parallel, managing the I/O order dependence can be a challenge. This article identifies some of these challenges and illustrates strategies for addressing them while maintaining parallel performance.

#### **Background**

Consider the problem of threading a video compression engine designed to perform real-time processing of uncompressed video from a live video source to disk or a network client. Clearly, harnessing the power of multiple processors is a key requirement in meeting the real-time requirements of such an application.

Video compression standards such as MPEG2 and MPEG4 are designed for streaming over unreliable links. Consequently, it easy to treat a single video stream as a sequence of smaller, standalone streams. One can achieve substantial speedups by processing these smaller streams in parallel. Some of the challenges in exploiting this parallelism through multithreading include the following:

- Defining non-overlapping subsets of the problem and assigning them to threads

- Ensuring that the input data is read exactly once and in the correct order

- Outputting blocks in the correct order, regardless of the order in which processing actually completes and without significant performance penalties

- Performing the above without a priori knowledge of the actual extent of the input data

In other situations, such as lossless data compression, it is often possible to determine the input data size in advance and explicitly partition the data into independent input blocks. The techniques outlined here apply equally well to this case.

#### **Advice**

The temptation might be to set up a chain of producers and consumers, but this approach is not scalable and is vulnerable to load imbalance. Instead, this article addresses each of the challenges above to achieve a more scalable design using data decomposition.

The approach taken here is to create a team of threads, with each thread reading a block of video, encoding it, and outputting it to a reorder buffer. Upon completion of each block, a thread returns to read and process the next block of video, and so on. This dynamic allocation of work minimizes load imbalance. The reorder buffer ensures that blocks of coded video are written in the correct order, regardless of their order of completion.

The original video encoding algorithm might take this form:

```

inFile = OpenFile ()

outFile == InitializeOutputFile ()

```

```

WriteHeader (outFile)

outputBuffer = AllocateBuffer (bufferSize)

while (frame = ReadNextFrame (inFile))

{

EncodeFrame (frame, outputBuffer)

if (outputBuffer size > bufferThreshold)

FlushBuffer(outputBuffer, outFile)

}

FlushBuffer (outputBuffer, outFile)

```

The first task is to replace the read and encode frame sequence with a block-based algorithm, setting up the problem for decomposition across a team of threads:

```

WriteHeader (outFile)

while (block = ReadNextBlock (inFile))

{

while(frame = ReadNextFrame (block))

{

EncodeFrame (frame, outputBuffer)

if (outputBuffer size > bufferThreshold)

FlushBuffer (outputBuffer, outFile)

}

FlushBuffer (outputBuffer, outFile)

}

```

The definition of a block of data will vary from one application to another, but in the case of a video stream, a natural block boundary might be the first frame at which a scene change is detected in the input, subject to constraints of minimum and maximum block sizes. Block-based processing requires allocation of an input buffer and minor changes to the source code to fill the buffer before processing. Likewise, the readNextFrame method must be changed to read from the buffer rather than the file.

The next step is to change the output buffering strategy to ensure that entire blocks are written as a unit. This approach simplifies output reordering substantially, since it is necessary only to ensure that the blocks are output in the correct order. The following code reflects the change to block-based output:

```

WriteHeader (outFile)

while (block = ReadNextBlock (inFile))

{

while (frame = ReadNextFrame (block))

{

EncodeFrame (frame, outputBuffer)

}

FlushBuffer (outputBuffer, outFile)

}

```

Depending on the maximum block size, a larger output buffer may be required.

Because each block is independent of the others, a special header typically begins each output block. In the case of an MPEG video stream, this header precedes a complete frame, known as an I-frame, relative to which future frames are defined. Consequently, the header is moved inside the loop over blocks:

```

while (block = ReadNextBlock (inFile))

{

WriteHeader (outputBuffer)

while (frame = ReadNextFrame (block))

{

EncodeFrame (frame, outputBuffer)

}

FlushBuffer (outputBuffer, outFile)

}

```

With these changes, it is possible to introduce parallelism using a thread library (i.e., Pthreads or the Win32 threading API) or OpenMP.

This is a simple but effective strategy for reading data safely and in order. Each thread acquires a lock, reads a block of data, then releases the lock. Sharing the input file ensures that blocks of data are read in order and exactly once. Because a ready thread always acquires the lock, the blocks are allocated to threads on a dynamic, or first-come-first-served basis, which typically minimizes load imbalance.

The final task is to ensure that blocks are output safely and in the correct order. A simple strategy would be to use locks and a shared output file to ensure that only one block is written at a time. This approach ensures thread-safety, but would allow the blocks to be output in something other than the original order. Alternately, threads could wait until all previous blocks have been written before flushing their output. Unfortunately, this approach introduces inefficiency because a thread sits idle waiting for its turn to write.

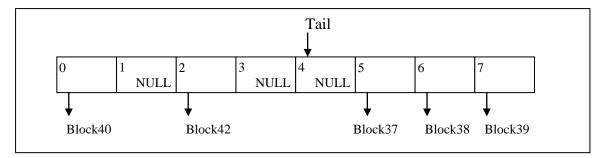

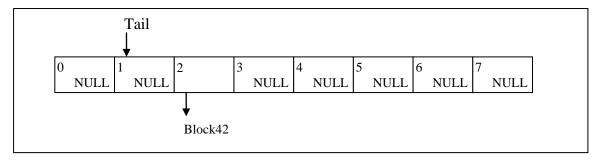

A better approach is to establish a circular reorder buffer for output blocks. Each block is assigned a sequential serial number. The "tail" of the buffer establishes the next block to be written. If a thread finishes processing a block of data other than that pointed to by the tail, it simply enqueues its block in the appropriate buffer position and returns to read and process the next available block. Likewise, if a thread finds that its just-completed block is that pointed to by the tail, it writes that block and any contiguous blocks that were previously enqueued. Finally, it updates the buffer's tail to point to the next block to be output. The reorder buffer allows completed blocks to be enqueued out-of-order, while ensuring they are written in order.

**Figure 1.** State of example reorder buffer before writing.

Figure 1 illustrates one possible state of the reorder buffer. Blocks 0 through 35 have already been processed and written, while blocks 37, 38, 39, 40 and 42 have been processed and are enqueued for writing. When the thread processing block 36 completes, it writes out blocks 36 through 40, leaving the reorder buffer in the state shown in Figure 2. Block 42 remains enqueued until block 41 completes.

**Figure 2.** State of example reorder buffer after writing.

Naturally, one needs to take certain precautions to ensure the algorithm is robust and fast:

- The shared data structures must be locked when read or written.

- The number of slots in the buffer must exceed the number of threads.

- Threads must efficiently wait, if an appropriate slot is not available in the buffer.

- Pre-allocate multiple output buffers per thread. This allows one to enqueue a pointer to the buffer and avoids extraneous data copies and memory allocations.

Using the output queue, the final algorithm is as follows:

```

{

EncodeFrame (frame, outputBuffer)

}

QueueOrFlush (outputBuffer, outFile)

}

```

This algorithm allows in-order I/O but still affords the flexibility of high performance, out-of-order parallel processing.

# **Usage Guidelines**

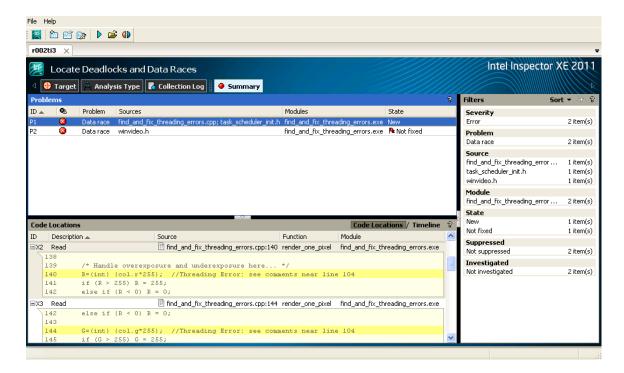

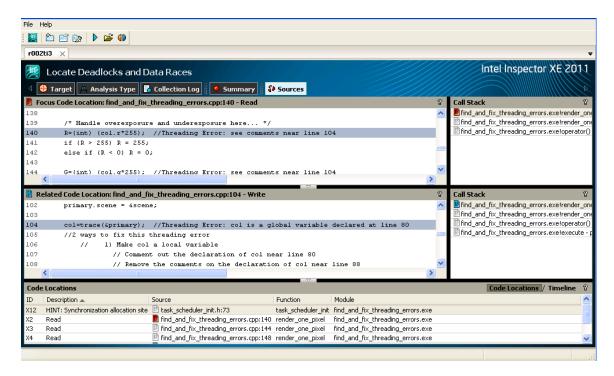

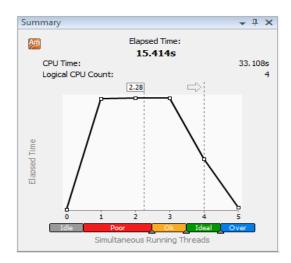

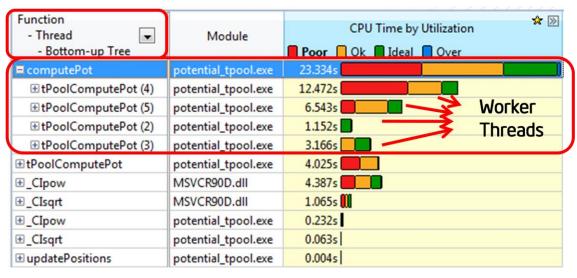

In some instances, the time to read and write data is comparable to the time required to process the data. In these cases, the following techniques may be beneficial: