## **SOLUTION BRIEF**

Telecommunications Server Performance

# Increase NFVi Performance and Flexibility

Offload processing from software to hardware to create efficiency with HCL's 50G Open vSwitch acceleration solution on the Intel® FPGA Programmable Acceleration Card (PAC) N3000.

## What Is the Intel FPGA PAC N3000?

The Intel FPGA Programmable Acceleration Card (Intel FPGA PAC) N3000 is a PAC that has the right memory mixture for network functions. It features an integrated network interface card (NIC) in a small form factor, and it enables high throughput, low latency, and low powerper-bit performance for custom networking pipelines. To help protect systems from FPGAhosted security exploits, the Intel FPGA PAC N3000 features a rootof-trust device that enables more secure loading of authorized workloads and board updates, and that enforces policies to help prevent unauthorized access to critical board interfaces and flash memory.

### **Eliminating the Performance Bottleneck**

In order to survive in a wildly competitive and ever-evolving industry, communications service providers (CoSPs) need to achieve the best performance possible, overcoming the bottlenecks that slow down their servers. With consistently growing numbers of subscribers, numbers of competitors, and advances in technology, the need for a CoSP to differentiate itself grows concurrently. The need for power efficiency is ever-present, as is the pressure to manage total cost of ownership (TCO) with cost-effective solutions. Intel and HCL had these challenges in mind when they collaborated on a joint solution that features Intel hardware and HCL software.

Using the Intel FPGA Programmable Acceleration Card (Intel FPGA PAC) N3000, HCL has created a solution that can dramatically increase performance and preserve flexibility for network functions virtualization infrastructure (NFVi) routing and switching. Open vSwitch (OvS) is a production-quality, multilayer virtual switch that can also implement a software-defined networking (SDN)-based approach that is crucial to creating a closed-loop, fully automated solution in NFVi. With aggressive software optimization to offload NFVi forwarding functionalities to the Intel FPGA PAC N3000, Intel and HCL have created a system that can provide the Intel FPGA-based solution, supported by selected NFVi suppliers.

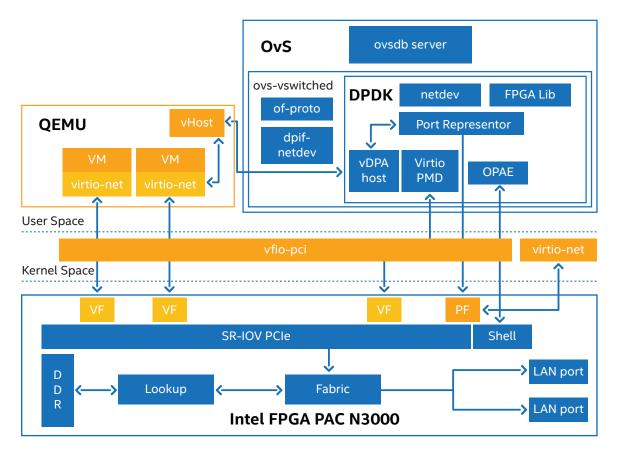

OvS can either forward packets through a kernel-based datapath or by using the Linux Data Plane Development Kit (DPDK). However, the kernel-based approach is not ideal for environments in which a high packet processing rate for short packets is required. OvS with DPDK (OvS-DPDK) enhances performance by using a fast path in user space through DPDK input/output (I/O) libraries (see Figure 1).

Several options are currently available that can help improve OvS performance by offloading partial or full processing to hardware. For example, with the OvS acceleration solution, the OvS data plane is fully offloaded to the Intel FPGA PAC N3000. Virtual datapath acceleration (vDPA) or passthrough allows virtual machines (VMs) to use standard virtio-net drivers (vendor independent 0.95 and 1.0) while the VMs are still directly connected to hardware. Speeding up firstpacket learning is crucial for NFVi to achieve telecommunications (telco)-grade performance while still optimizing TCO. This improvement is achieved by a new approach called in-band packet management.

In OvS, two major components deal with packet forwarding: ovs-vswitchd and the datapath cache. The ovs-vswitchd component is a user-space daemon that can instruct the datapath component on how to forward a received packet. When a packet does not match any rule in the datapath, the packet is delivered to ovs-vswitchd, which then installs a specific rule into the hardware datapath cache to

#### Figure 1. The OvS acceleration solution Data Plane Development Kit (DPDK) architecture overview

handle subsequent packets (this is called the "learning phase"). Two options are possible when it comes to the datapath cache: it can be either kernel-based (using FPGA configuration status registers [CSRs]) or DPDK-based through in-band; HCL's OvS acceleration solution fully supports both options.

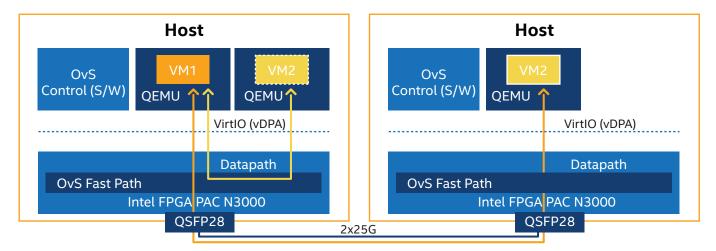

#### Scale-in/Scale-out Using Live Migration

The ability to migrate workloads in real time is one of the key differentiators between network functions virtualization (NFV) environments and legacy ones. The OvS acceleration solution achieves this ability by implementing a specific QEMU API that can track VM content from the hardware accelerator.

#### Figure 2. Datapath after migration

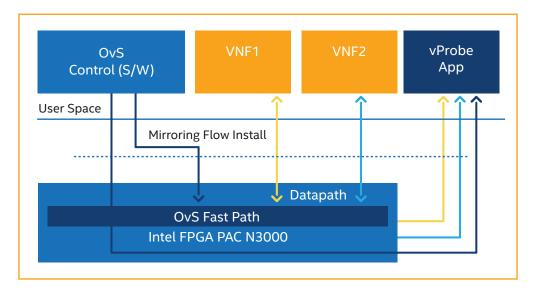

#### Service Assurance with Port Mirroring

Strong service assurance is critical in a transformation to a software-defined and increasingly virtualized network environment. It is vital to monitor service-level parameters and identify any malfunctions that could lead to service disruption in real time, so that orchestrators can act quickly to re-establish functionalities. In a virtualized environment, these activities are even more challenging as a result of the disaggregation of hardware and software and the ability to deploy services dynamically. In telco environments, vProbes perform network monitoring on millions of specific flows and are vital in measuring service key performance indicators (KPIs). Closed-loop automation can make use of vProbe information to trigger artificial intelligence (AI)/machine learning (ML) algorithms for analyzing networks, evaluating healing strategies and possible optimizations. The Intel and HCL solution supports traffic duplication at the microflow level, supporting entries in the millions, including virtual network function (VNF)-to-VNF/VNF-to-host for virtual network TAP (vTAP) communications, debugging, and legal intercept with no performance loss. This is achieved by inserting OvS mirroring rules directly in the hardware fast path, with vProbes directly connected to hardware.

#### Figure 3. Flow mirroring to vProbe

#### **Key Features and Roadmap**

The OvS acceleration solution by HCL, enabled by the Intel FPGA PAC N3000, currently supports the features and functionality shown in Table 1, with additional features on the horizon.

#### Table 1. Intel FPGA PAC N3000—2 x 25G OvS acceleration solution feature roadmap

|                         | Intel reference design features                                                                                                                                                      | Enhanced OvS features (proposed)—Phase 1                             |                                                                                                                                                                      | Advanced features<br>(proposed)—Phase 2                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host IF                 | <ul> <li>VirtIO 1.0 (0.95 with vDPA)</li> <li>Multiple Qs/virtual function (VF)</li> <li>Live migration</li> <li>Virtio-net PF</li> </ul>                                            |                                                                      |                                                                                                                                                                      | <ul> <li>9K jumbo frames (burst<br/>memory + CCB)</li> </ul>                                                                                                 |

| Network                 | <ul> <li>OvS: Virtual Extensible LAN<br/>(VXLAN)/TEP without Link<br/>Aggregation Control Protocol<br/>(LACP)</li> <li>OvS: VXLAN/TEP with LACP</li> <li>Checksum offload</li> </ul> | <ul> <li>IPv4 tunneling<br/>support</li> </ul>                       | <ul> <li>L2VPN/L3VPN</li> <li>IPv6 tunneling support</li> <li>Virtual LAN (VLAN)<br/>port support</li> </ul>                                                         |                                                                                                                                                              |

| Management              | <ul> <li>OvS v2.9.2 kernel<br/>MBO-based logic</li> </ul>                                                                                                                            | <ul> <li>Flow update<br/>rate—500K</li> <li>VXLAN routing</li> </ul> | <ul> <li>DPDK in-band/kernel<br/>custom MBO in-band<br/>specific control path</li> <li>Flow table update—<br/>DPDK-based 500K<br/>frames per second (fps)</li> </ul> | • Flow update<br>rate—1M                                                                                                                                     |

| Pipeline<br>Improvement | <ul> <li>Rate limiting per VF</li> <li>Queue scheduling</li> </ul>                                                                                                                   | Service assurance     with port mirroring                            |                                                                                                                                                                      | <ul> <li>Bi-directional quality<br/>of service (QoS)</li> <li>Megaflow offload</li> <li>CT security group</li> <li>Hardware multicast<br/>support</li> </ul> |

#### **Groundbreaking Performance for the Next Generation**

Intel and HCL have addressed the NFVi industry challenge of power efficiency and performance with the hardwareoffloaded OvS acceleration solution using the Intel FPGA PAC N3000. By using generic or standard interfaces, there is no need to configure specific modifications to run telco functions. With a dynamic, and often increasing, number of users to accommodate, the ability to scale-in and scale-out is crucial for live migration. With the Intel FPGA PAC N3000 card, customers can now offload processing from software to hardware, saving CPU cores and creating valuable efficiency.

To learn more about the Intel FPGA PAC N3000, visit: intel.com/pacn3000

To learn more about NFV acceleration solutions, visit: intel.com/content/www/us/en/wireline/products/programmable/ applications/nfv.html

To learn more about HCL, visit: hcltech.com/

#### About HCL

HCL Technologies is a next-generation global technology company that helps enterprises reimagine their businesses for the digital age. With a strong portfolio of services and solutions in the embedded and edge computing space, HCL offers world-class products and solutions such as NFV acceleration, enabling global companies across industries to generate tangible business value from their Internet of Things (IoT) and 5G investments. For more information, see **hcltech.com**.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. **No product or component can be absolutely secure**.

Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings release and SEC filings at intc.com.

Your costs and results may vary.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

0320/YR/PRW/PDF

Printed in USA