# High Definition Audio Specification Revision 1.0a

June 17, 2010

# **Revision History**

| Revision | Purpose                                                                                                                                                                                                                                            | Date           |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.0      | Initial Release                                                                                                                                                                                                                                    | April 15, 2004 |

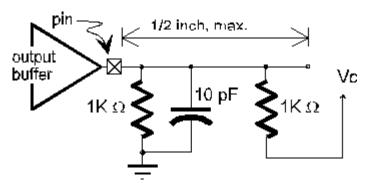

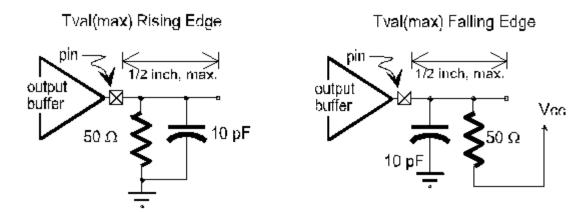

| 1.0a     | Updated with DCN No: HDA001-A changes.                                                                                                                                                                                                             | June 17, 2010  |

|          | Updated with DCN No: HDA002-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA006-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA011-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA012-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA015-B changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA016-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA017-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA019-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA022-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA024-A changes.                                                                                                                                                                                                             |                |

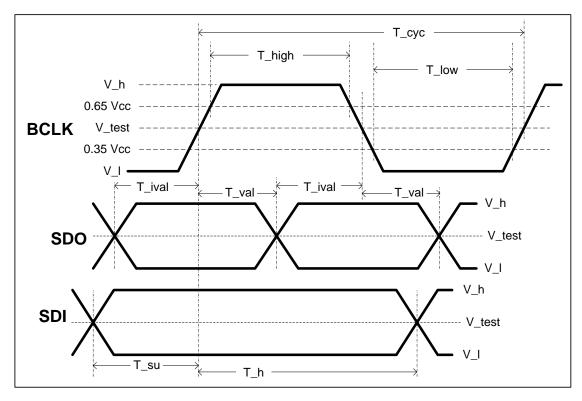

|          | Updated with DCN No: HDA034-A2 changes.                                                                                                                                                                                                            |                |

|          | Updated with DCN No: HDA035-A changes.                                                                                                                                                                                                             |                |

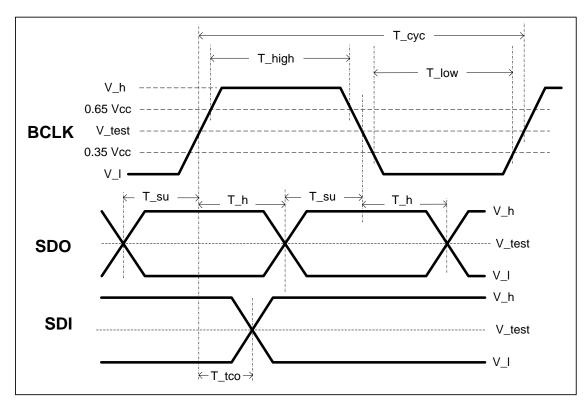

|          | Updated with DCN No: HDA036-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA039-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA041-A changes.                                                                                                                                                                                                             |                |

|          | Updated with DCN No: HDA042-A changes.                                                                                                                                                                                                             |                |

|          | Errata:                                                                                                                                                                                                                                            |                |

|          | <ul> <li>Clarified Input Payload Capability and Output Payload<br/>Capability Reset value is implementation specific.</li> </ul>                                                                                                                   |                |

|          | <ul> <li>Clarified that Stream Descriptor n FIFO Size must be valid<br/>and static after every programming of data format register,<br/>as well as when RUN bit is set.</li> </ul>                                                                 |                |

|          | <ul> <li>Clarified that Stream Descriptor n BDL Pointer Upper Base<br/>Address register attribute is RO if not supporting 64 bit<br/>addressing.</li> </ul>                                                                                        |                |

|          | <ul> <li>Fixed timing error in "Codec Discovery" section that SW<br/>should wait for at least 521 us (25 frames) after reading<br/>CRST# as '1' before accessing codec.</li> </ul>                                                                 |                |

|          | • Strongly recommend the default value for EAPD to be '1' in "EAPD/BTL Enable" section.                                                                                                                                                            |                |

|          | <ul> <li>Clarified the codec response expected for double Function<br/>Group reset command in D3cold state, but recommended<br/>no response for the first Function Group reset of the double<br/>Function Group reset command sequence.</li> </ul> |                |

|          | <ul> <li>Clarified the reset value for FIFOS register is<br/>implementation specific.</li> </ul>                                                                                                                                                   |                |

|          | <ul> <li>Clarified UR enable verb for function group node is<br/>conditional in the required support for verbs table.</li> </ul>                                                                                                                   |                |

# **Legal Notice**

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein, except that a license is hereby granted to copy and reproduce this specification for internal use only. Intel assumes no responsibility for any errors contained in this document and has no liabilities or obligations for any damages arising from or in connection with the use of this document.

Intel may make changes to specifications, product descriptions, and plans at any time, without notice.

Intel may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

\*Other names and brands may be claimed as the property of others.

Copyright © 2003-2010, Intel Corporation. All rights reserved.

# **Contents**

| 1 | Intr | oductio    | on                                                        | 16 |

|---|------|------------|-----------------------------------------------------------|----|

|   | 1.1  | Scope a    | and Layout of This Document                               | 16 |

|   | 1.2  |            | on and Goals                                              |    |

|   |      | 1.2.1      | AC'97 Compatibility                                       | 17 |

|   |      | 1.2.2      | Feature List                                              | 17 |

|   |      | 1.2.3      | Related Documents                                         | 17 |

| 2 | Arc  | hitectu    | re Overview                                               | 18 |

|   | 2.1  | Hardwa     | re System Overview                                        | 18 |

|   | 2.2  | Streams    | s and Channels                                            | 19 |

|   | 2.3  | DMA CI     | hannel Operation                                          | 21 |

|   | 2.4  | Initializa | ation and Enumeration                                     | 22 |

| 3 | Reg  | gister In  | nterface                                                  | 24 |

|   | 3.1  | Introduc   | ction to Controller Registers                             | 24 |

|   |      | 3.1.1      | Terminology                                               | 24 |

|   |      | 3.1.2      | General Register Behaviors and Access Requirements        | 24 |

|   |      | 3.1.3      | Behavior With 64-bit Addresses                            |    |

|   | 3.2  |            | efinition Audio Controller System Bus Interface Registers |    |

|   | 3.3  | High De    | efinition Audio Controller Register Set                   |    |

|   |      | 3.3.1      | Global Capabilities, Status, and Control                  |    |

|   |      | 3.3.2      | Offset 00h: GCAP – Global Capabilities                    |    |

|   |      | 3.3.3      | Offset 02h: VMIN – Minor Version                          |    |

|   |      | 3.3.4      | Offset 03h: VMAJ – Major Version                          |    |

|   |      | 3.3.5      | Offset 04h: OUTPAY – Output Payload Capability            |    |

|   |      | 3.3.6      | Offset 06h: INPAY - Input Payload Capability              |    |

|   |      | 3.3.7      | Offset 08h: GCTL – Global Control                         |    |

|   |      | 3.3.8      | Offset 0Ch: WAKEEN – Wake Enable                          |    |

|   |      | 3.3.9      | Offset 0Eh: STATESTS – State Change Status                | 32 |

|   |      | 3.3.10     | Offset 10h: GSTS – Global Status                          |    |

|   |      | 3.3.11     | Offset 18h: OUTSTRMPAY – Output Stream Payload Capability |    |

|   |      | 3.3.12     | Offset 1Ah: INSTRMPAY – Input Stream Payload Capability   |    |

|   |      | 3.3.13     | Interrupt Status and Control                              |    |

|   |      | 3.3.14     | Offset 20h: INTCTL – Interrupt Control                    |    |

|   |      | 3.3.15     | Offset 24h: INTSTS – Interrupt Status                     |    |

|   |      | 3.3.16     | Offset 30h: Wall Clock Counter                            |    |

|   |      | 3.3.17     | Offset 38h: SSYNC – Stream Synchronization                |    |

|   |      | 3.3.18     | Offset 40h: CORB Lower Base Address                       | 36 |

|   |      | 3.3.19     | Offset 44h: CORBUBASE – CORB Upper Base Address           | 36 |

|   |      | 3.3.20     | Offset 48h: CORBWP – CORB Write Pointer                   |    |

|   |      | 3.3.21     | Offset 4Ah: CORBRP – CORB Read Pointer                    |    |

|   |      | 3.3.22     | Offset 4Ch: CORBCTL – CORB Control                        |    |

|   |      | 3.3.23     | Offset 4Dh: CORBSTS – CORB Status                         |    |

|   |      | 3.3.24     | Offset 4Eh: CORBSIZE – CORB Size                          |    |

|   |      | 3.3.25     | Offset 50h: RIRBLBASE – RIRB Lower Base Address           | 39 |

|   |     | 3.3.26    | Offset 54h: RIRBUBASE – RIRB Upper Base Address                          |          |

|---|-----|-----------|--------------------------------------------------------------------------|----------|

|   |     | 3.3.27    | Offset 58h: RIRBWP – RIRB Write Pointer                                  |          |

|   |     | 3.3.28    | Offset 5Ah: RINTCNT – Response Interrupt Count                           | 40       |

|   |     | 3.3.29    | Offset 5Ch: RIRBCTL – RIRB Control                                       |          |

|   |     | 3.3.30    | Offset 5Dh: RIRBSTS – RIRB Status                                        |          |

|   |     | 3.3.31    | Offset 5Eh: RIRBSIZE – RIRB Size                                         |          |

|   |     | 3.3.32    | Offset 70h: DPLBASE – DMA Position Lower Base Address                    |          |

|   |     | 3.3.33    | Offset 74h: DPUBASE – DMA Position Upper Base Address                    |          |

|   |     | 3.3.34    | Stream Descriptors                                                       | 43       |

|   |     | 3.3.35    | Offset 80: {IOB}SDnCTL – Input/Output/Bidirectional Stream Descriptor n  | )        |

|   |     |           | Control                                                                  | 43       |

|   |     | 3.3.36    | Offset 83h: {IOB}SD0STS – Input/Output/Bidirectional Stream Descriptor   | n        |

|   |     |           | Status                                                                   | 45       |

|   |     | 3.3.37    | Offset 84: {IOB}SDnLPIB – Input/Output/Bidirectional Stream Descriptor / | n        |

|   |     |           | Link Position in Buffer                                                  | 46       |

|   |     | 3.3.38    | Offset 88: {IOB}SDnCBL - Input/Output/Bidirectional Stream Descriptor n  | )        |

|   |     |           | Cyclic Buffer Length                                                     | 46       |

|   |     | 3.3.39    | Offset 8C: {IOB}ISDnLVI - Input/Output/Bidirectional Stream Descriptor n | )        |

|   |     |           | Last Valid Index                                                         |          |

|   |     | 3.3.40    | Offset 90: {IOB}SDnFIFOS - Input/Output/Bidirectional Stream Descriptor  |          |

|   |     |           | FIFO Size                                                                | 47       |

|   |     | 3.3.41    | Offset 92: {IOB}SDnFMT – Input/Output/Bidirectional Stream Descriptor r  |          |

|   |     |           | Format                                                                   | 47       |

|   |     | 3.3.42    | Offset 98h: {IOB}SDnBDPL - Input/Output/Bidirectional Stream Descripto   |          |

|   |     |           | BDL Pointer Lower Base Address                                           |          |

|   |     | 3.3.43    | Offset 9Ch: {IOB}SDnBDPU - Input/Output/Bidirectional Stream Descripted  |          |

|   |     |           | BDL Pointer Upper Base Address                                           |          |

|   |     | 3.3.44    | Offset 2030h: WALCLKA – Wall Clock Counter Alias                         |          |

|   |     | 3.3.45    | Offset 2084, 20A4,: {IOB}SDnLICBA - Input/Output/Bidirectional Stream    | ım       |

|   |     |           | Descriptor <i>n</i> Link Position in Buffer Alias                        |          |

|   | 3.4 |           | te Command Input and Output Registers                                    |          |

|   |     | 3.4.1     | Offset 60h: Immediate Command Output Interface                           |          |

|   |     | 3.4.2     | Offset 64h: Immediate Response Input Interface                           |          |

|   |     | 3.4.3     | Offset 68h: Immediate Command Status                                     |          |

|   |     |           | Structure                                                                |          |

|   | 3.6 | Data Str  | uctures                                                                  |          |

|   |     | 3.6.1     | DMA Position in Current Buffer                                           |          |

|   |     | 3.6.2     | Buffer Descriptor List                                                   |          |

|   |     | 3.6.3     | Buffer Descriptor List Entry                                             |          |

|   |     | 3.6.4     | Command Output Ring Buffer                                               |          |

|   |     | 3.6.5     | Response Input Ring Buffer                                               |          |

|   | 3.7 | Codec V   | erb and Response Structures                                              |          |

|   |     | 3.7.1     | Stream Format Structure                                                  | 58       |

|   | Pro | grammi    | ng Model                                                                 | 61       |

| 1 |     | _         | _                                                                        |          |

| 1 |     | Theory    | ot ()neration                                                            | 61       |

| 1 | 4.1 |           | of Operation                                                             |          |

| + |     | Controlle | er Initialization                                                        | 61       |

| 1 | 4.1 |           |                                                                          | 61<br>61 |

|          | 4.3  | Codec [ | Discovery. |                                          | 62 |

|----------|------|---------|------------|------------------------------------------|----|

|          | 4.4  | Codec ( |            | and Control                              |    |

|          |      | 4.4.1   | Comman     | d Outbound Ring Buffer – CORB            | 62 |

|          |      |         | 4.4.1.1    | CORB Buffer Allocation                   |    |

|          |      |         | 4.4.1.2    | CORB Entry Format                        | 64 |

|          |      |         | 4.4.1.3    | Initializing the CORB                    | 64 |

|          |      |         | 4.4.1.4    | Transmitting Commands via the CORB       | 65 |

|          |      |         | 4.4.1.5    | Other CORB Programming Notes             | 66 |

|          |      | 4.4.2   | Response   | e Inbound Ring Buffer - RIRB             | 66 |

|          |      |         | 4.4.2.1    | RIRB Entry Format:                       | 67 |

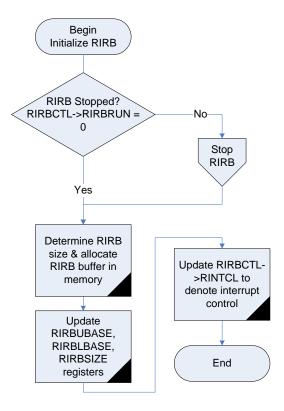

|          |      |         | 4.4.2.2    | Initializing the RIRB                    | 68 |

|          | 4.5  | Stream  | Manageme   | ent                                      | 69 |

|          |      | 4.5.1   | Stream D   | Data In Memory                           | 69 |

|          |      | 4.5.2   | Configuri  | ng and Controlling Streams               | 70 |

|          |      | 4.5.3   | Starting S | Streams                                  | 70 |

|          |      | 4.5.4   | Stopping   | Streams                                  | 71 |

|          |      | 4.5.5   | Resuming   | g Streams                                | 71 |

|          |      | 4.5.6   | Stream S   | Steady State Operation                   | 71 |

|          |      | 4.5.7   |            | nization                                 |    |

|          |      |         | 4.5.7.1    | Controller to Controller Synchronization | 72 |

|          |      |         | 4.5.7.2    | Stream to Stream Start Synchronization   | 72 |

|          |      |         | 4.5.7.3    | Stream to Stream Stop Synchronization    | 73 |

|          |      | 4.5.8   | Power Ma   | anagement                                | 73 |

|          |      |         | 4.5.8.1    | Power State Transitions                  | 73 |

|          |      |         | 4.5.8.2    | Power Optimization                       | 73 |

|          |      | 4.5.9   | Codec W    | ′ake                                     | 74 |

|          |      |         | 4.5.9.1    | Codec Wake From System S0, Controller D0 | 74 |

|          |      |         | 4.5.9.2    | Codec Wake From System S0, Controller D3 | 74 |

|          |      |         | 4.5.9.3    | Codec Wake From System S3                | 74 |

|          |      |         | 4.5.9.4    | Checking Wake Status on Resume           | 74 |

| 5        | امنا | . Duata |            | •                                        | 77 |

| <b>O</b> |      |         |            |                                          |    |

|          | 5.1  |         |            |                                          |    |

|          | 5.2  | _       |            |                                          |    |

|          |      | 5.2.1   | _          | efinitions                               |    |

|          |      | 5.2.2   |            | ı Topology                               |    |

|          |      |         | 5.2.2.1    | Basic System                             |    |

|          |      |         | 5.2.2.2    | Bandwidth Scaling                        |    |

|          |      | 5.2.3   |            | Signal Timing                            |    |

|          | 5.3  |         |            | on                                       |    |

|          |      | 5.3.1   |            | ame Components                           |    |

|          |      | 5.3.2   |            | rame Formatting                          |    |

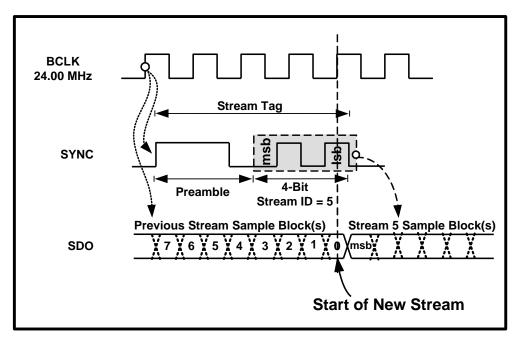

|          |      |         | 5.3.2.1    | Outbound Stream Tags                     |    |

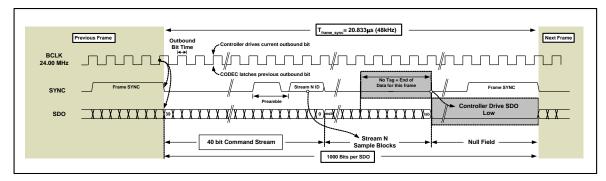

|          |      |         | 5.3.2.2    | Outbound Frame Overview – Single SDO     |    |

|          |      |         | 5.3.2.3    | Outbound Frame Overview – Multiple SDO   |    |

|          |      | 5.3.3   |            | me Formatting                            |    |

|          |      |         | 5.3.3.1    | Inbound Stream Tags                      |    |

|          |      |         | 5.3.3.2    | Zero Padding Inbound Stream Packets      |    |

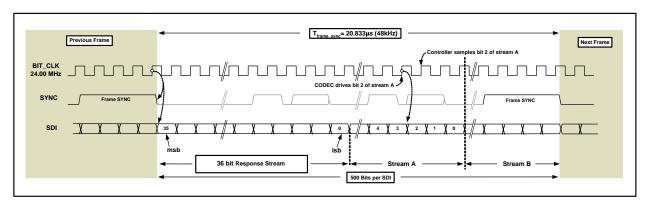

|          |      |         | 5.3.3.3    | Inbound Frame Overview                   | 90 |

|   |       |                | 5.3.3.4    |                                                  |     |

|---|-------|----------------|------------|--------------------------------------------------|-----|

|   | 5.4   |                |            | dependent Sample Rates                           |     |

|   |       | 5.4.1          |            | mple Rendering Timing                            |     |

|   |       | 5.4.2          |            | ole Delivery Timing                              |     |

|   |       | 5.4.3          |            | nchronous Input                                  |     |

|   | 5.5   |                |            | tion                                             |     |

|   |       | 5.5.1          |            | t                                                |     |

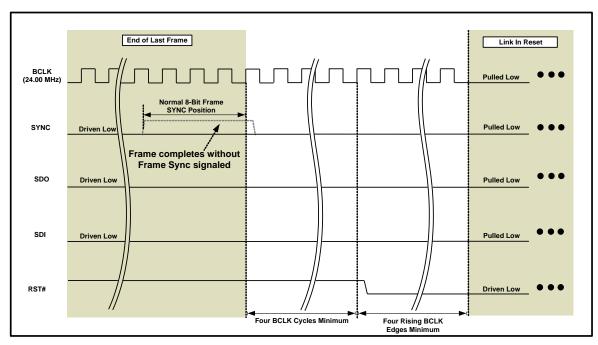

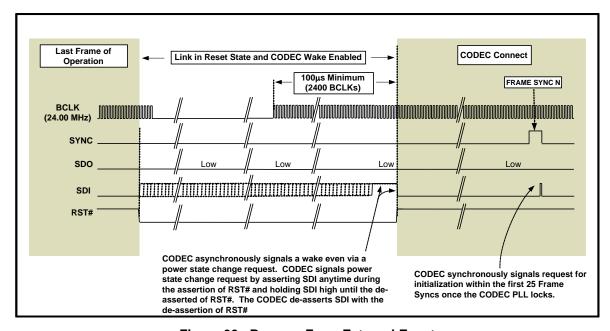

|   |       |                | 5.5.1.1    | Entering Link Reset                              |     |

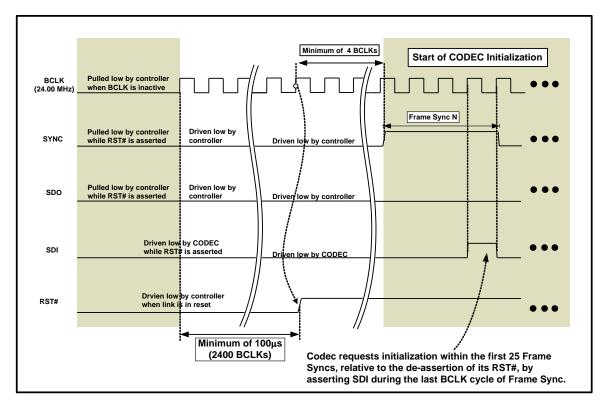

|   |       |                | 5.5.1.2    | Exiting Link Reset                               |     |

|   |       | 5.5.2          |            | nction Group Reset                               |     |

|   |       | 5.5.3          |            | ialization                                       | 97  |

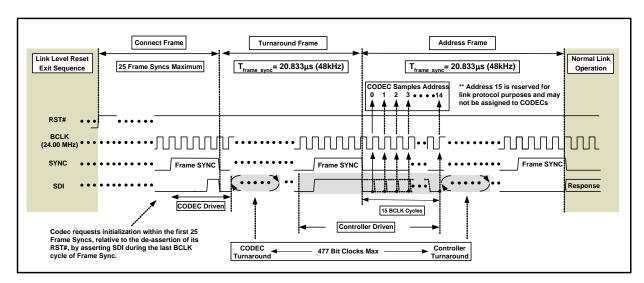

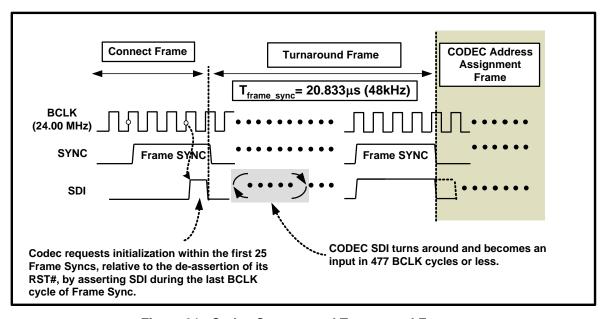

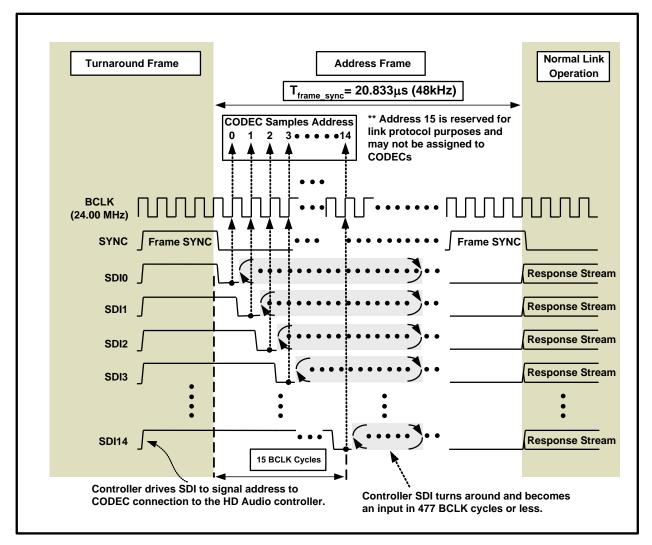

|   |       |                | 5.5.3.1    | Connect and Turnaround Frames                    |     |

|   |       |                | 5.5.3.2    | Address Frame                                    |     |

|   |       |                | 5.5.3.3    | Multi-SDI Codec Initialization                   |     |

|   | F 6   | Dower M        | 5.5.3.4    | Un-initialized and Partially Initialized Codecst |     |

|   | 5.6   | Power iv       | ianagemen  | ll                                               | 101 |

| 6 | Elec  | ctrical Ir     | nterface.  |                                                  | 105 |

|   | 6.1   |                |            |                                                  |     |

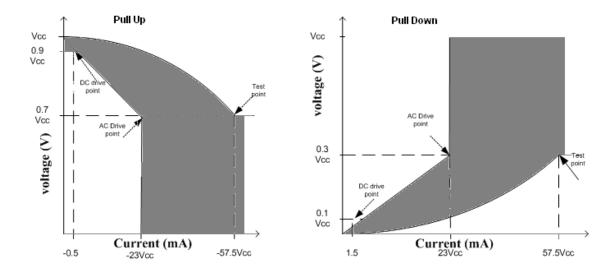

|   | • • • | 6.1.1          |            | w Voltage (1.5V) Transition                      |     |

|   | 6.2   | 3.3V Sig       |            | ronment                                          |     |

|   |       | 6.2.1          |            | ications                                         |     |

|   |       | 6.2.2          |            | ications                                         |     |

|   |       | 6.2.3          | Maximum    | AC Ratings and Device Protection                 | 109 |

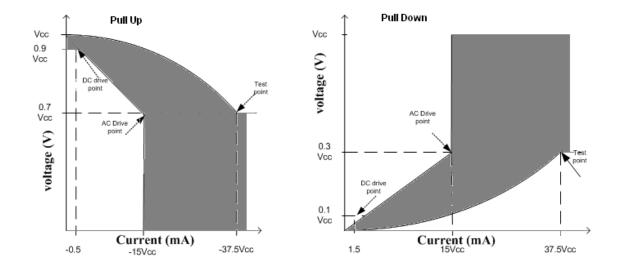

|   | 6.3   | Low Volt       | age Signal | ing Environment                                  | 110 |

|   |       | 6.3.1          | DC Specif  | ications                                         | 110 |

|   |       | 6.3.2          |            | ications                                         |     |

|   |       | 6.3.3          |            | AC Ratings and Device Protection                 |     |

|   | 6.4   |                |            | Test Conditions                                  |     |

|   | 6.5   | _              |            | າ                                                |     |

|   |       | 6.5.1          |            | rameters                                         |     |

|   | 6.6   |                |            | pecification                                     |     |

|   | 6.7   |                |            | ard) Specification                               |     |

|   | 6.8   |                |            | ts                                               |     |

|   | 6.9   | •              | •          | get                                              |     |

|   | 6.10  | 6.10.1         |            | ents<br>pard Impedance                           |     |

|   |       | 6.10.1         |            | idelines                                         |     |

|   |       | 6.10.3         |            | gth Limits                                       |     |

|   | 6.11  |                |            | utions                                           |     |

|   |       |                |            | isms                                             |     |

| _ |       |                |            |                                                  |     |

| 7 |       |                |            | I Requirements                                   |     |

|   | 7.1   |                |            |                                                  |     |

|   |       | 7.1.1          |            | rchitecture                                      |     |

|   |       | 7.1.2          |            | ressing                                          |     |

|   | 7.0   | 7.1.3          |            | erconnection Rules                               |     |

|   | 7.2   |                |            | efinition                                        |     |

|   |       | 7.2.1<br>7.2.2 | Function 6 | )<br>Pround                                      | 132 |

|   |       | 1//            | FUNCTION G | 71000S                                           | エマン |

|     |         | 7.2.2.1    | Audio Function Group                                    | 132 |

|-----|---------|------------|---------------------------------------------------------|-----|

|     |         | 7.2.2.2    | Vendor Specific Modem Function Group                    | 133 |

|     | 7.2.3   | Widgets    |                                                         | 134 |

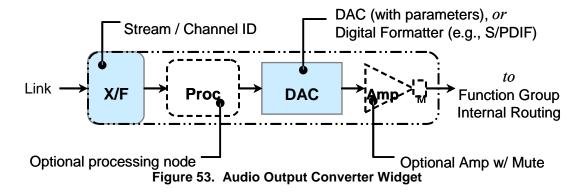

|     |         | 7.2.3.1    | Audio Output Converter Widget                           | 134 |

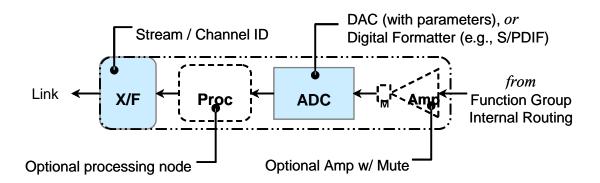

|     |         | 7.2.3.2    | Audio Input Converter Widget                            |     |

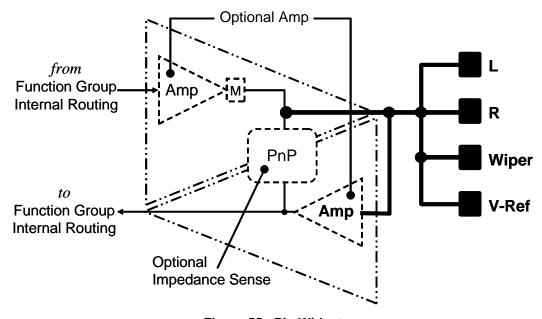

|     |         | 7.2.3.3    | Pin Widget                                              | 136 |

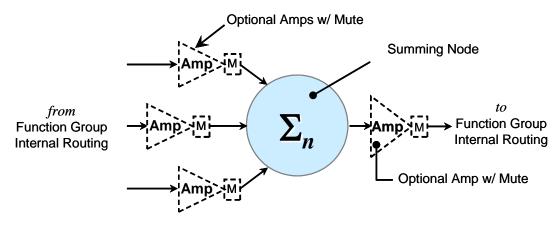

|     |         | 7.2.3.4    | Mixer (Summing Amp) Widget                              | 137 |

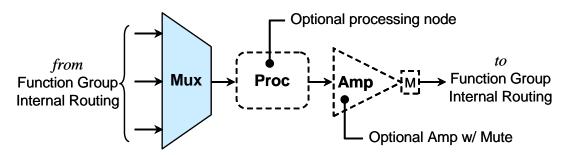

|     |         | 7.2.3.5    | Selector (Multiplexer) Widget                           | 137 |

|     |         | 7.2.3.6    | Power Widget                                            | 138 |

|     |         | 7.2.3.7    | Volume Knob Widget                                      | 138 |

|     |         | 7.2.3.8    | Beep Generator Widget                                   | 138 |

| 7.3 | Codec F | Parameters | and Controls                                            | 139 |

|     | 7.3.1   | Required   | Verb Response                                           | 139 |

|     | 7.3.2   |            | DI Operation                                            |     |

|     | 7.3.3   | Controls   |                                                         | 141 |

|     |         | 7.3.3.1    | Get Parameter                                           | 141 |

|     |         | 7.3.3.2    | Connection Select Control                               | 141 |

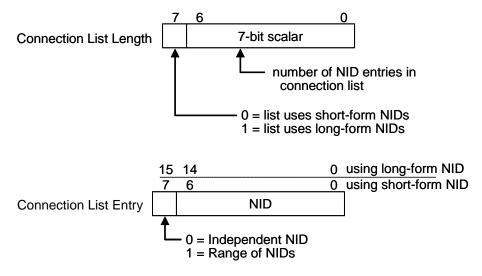

|     |         | 7.3.3.3    | Get Connection List Entry                               | 142 |

|     |         | 7.3.3.4    | Processing State                                        | 143 |

|     |         | 7.3.3.5    | Coefficient Index                                       |     |

|     |         | 7.3.3.6    | Processing Coefficient                                  | 145 |

|     |         | 7.3.3.7    | Amplifier Gain/Mute                                     |     |

|     |         | 7.3.3.8    | Converter Format                                        | 147 |

|     |         | 7.3.3.9    | Digital Converter Control                               |     |

|     |         | 7.3.3.10   | Power State                                             |     |

|     |         | 7.3.3.11   | Converter Stream, Channel                               | 159 |

|     |         | 7.3.3.12   | Input Converter SDI Select                              | 160 |

|     |         | 7.3.3.13   | Pin Widget Control                                      |     |

|     |         | 7.3.3.14   | Unsolicited Response                                    | 162 |

|     |         |            | 7.3.3.14.1 Intrinsic Unsolicited Responses              | 163 |

|     |         |            | 7.3.3.14.2 Non-Intrinsic Unsolicited Response - Content |     |

|     |         |            | Protection                                              | 164 |

|     |         | 7.3.3.15   | Pin Sense                                               | 165 |

|     |         | 7.3.3.16   | EAPD/BTL Enable                                         | 167 |

|     |         | 7.3.3.17   | GPI Data                                                | 169 |

|     |         | 7.3.3.18   | GPI Wake Enable Mask                                    | 169 |

|     |         | 7.3.3.19   | GPI Unsolicited Enable Mask                             | 170 |

|     |         | 7.3.3.20   | GPI Sticky Mask                                         | 170 |

|     |         | 7.3.3.21   | GPO Data                                                | 171 |

|     |         | 7.3.3.22   | GPIO Data                                               | 171 |

|     |         | 7.3.3.23   | GPIO Enable Mask                                        | 172 |

|     |         | 7.3.3.24   | GPIO Direction                                          |     |

|     |         | 7.3.3.25   | GPIO Wake Enable Mask                                   |     |

|     |         | 7.3.3.26   | GPIO Unsolicited Enable Mask                            |     |

|     |         | 7.3.3.27   | GPIO Sticky Mask                                        |     |

|     |         | 7.3.3.28   | Beep Generation                                         |     |

|     |         | 7.3.3.29   | Volume Knob                                             |     |

|     |         | 7.3.3.30   | Implementation Identification                           |     |

|     |         | 7.3.3.31   | Configuration Default                                   | 177 |

|     |         |            |                                                         |     |

|     |         | 7.3.3.32          | Stripe Control                                       | 182 |

|-----|---------|-------------------|------------------------------------------------------|-----|

|     |         | 7.3.3.33          | Function Reset                                       | 182 |

|     |         | 7.3.3.34          | EDID-Like Data (ELD) Data                            | 183 |

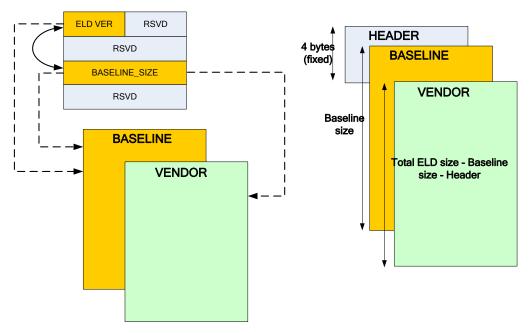

|     |         |                   | 7.3.3.34.1 ELD Memory Structure                      |     |

|     |         | 7.3.3.35          | Converter Channel Count                              |     |

|     |         | 7.3.3.36          | Data Island Packet – Size info (DIP-Size)            |     |

|     |         | 7.3.3.37          | Data Island Packet – Index (DIP-Index)               |     |

|     |         | 7.3.3.38          | Data Island Packet – Data (DIP-Data)                 |     |

|     |         | 7.3.3.39          | Data Island Packet – Transmit Control (DIP-XmitCtrl) |     |

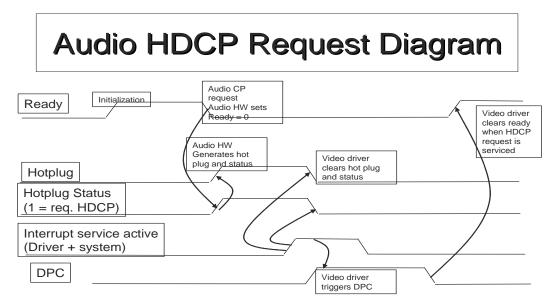

|     |         | 7.3.3.40          | Content Protection Control (CP_CONTROL)              | 194 |

|     |         | 7.3.3.41          | Audio Sample Packet (ASP) Channel Mapping            |     |

|     | 7.3.4   | Paramete          | ers                                                  | 198 |

|     |         | 7.3.4.1           | Vendor ID                                            | 198 |

|     |         | 7.3.4.2           | Revision ID                                          | 198 |

|     |         | 7.3.4.3           | Subordinate Node Count                               |     |

|     |         | 7.3.4.4           | Function Group Type                                  | 199 |

|     |         | 7.3.4.5           | Audio Function Group Capabilities                    | 200 |

|     |         | 7.3.4.6           | Audio Widget Capabilities                            |     |

|     |         | 7.3.4.7           | Supported PCM Size, Rates                            |     |

|     |         |                   | 7.3.4.7.1 HDMI LPCM CAD (Obsolete)                   |     |

|     |         | 7.3.4.8           | Supported Stream Formats                             |     |

|     |         | 7.3.4.9           | Pin Capabilities                                     |     |

|     |         | 7.3.4.10          | Amplifier Capabilities                               |     |

|     |         | 7.3.4.11          | Connection List Length                               |     |

|     |         | 7.3.4.12          | Supported Power States                               |     |

|     |         | 7.3.4.13          | Processing Capabilities                              |     |

|     |         | 7.3.4.14          | GP I/O Count                                         |     |

|     |         | 7.3.4.15          | Volume Knob Capabilities                             |     |

|     | 7.3.5   |                   | efined Verbs                                         |     |

|     | 7.3.6   |                   | Parameter and Control Support                        |     |

| 7.4 | Packag  |                   | ernal Circuits                                       |     |

|     | 7.4.1   |                   | Audio 48-Pin Codec Packages                          |     |

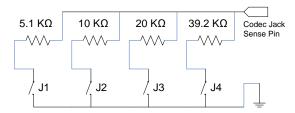

|     | 7.4.2   |                   | ck Detection Circuits                                |     |

| 7.5 |         |                   | agement Requirements                                 |     |

| 7.6 | Testing | <b>Provisions</b> |                                                      | 222 |

# **Figures**

| Figure 1.  | High Definition Audio Architecture Block Diagram    | .18 |

|------------|-----------------------------------------------------|-----|

|            | Streams                                             |     |

| Figure 3.  | Conceptual Frame Composition                        | .21 |

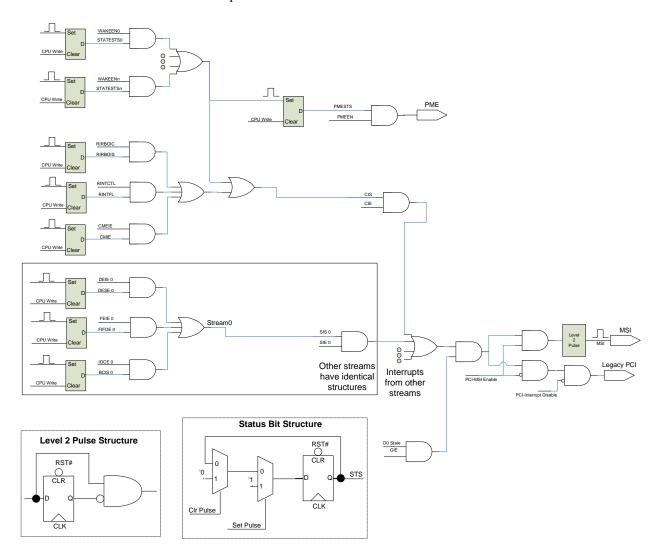

| Figure 4:  | Controller Interrupt Structure                      | .54 |

| Figure 5.  | Verb Format                                         | .57 |

| Figure 6.  | Solicited Response Format                           | .57 |

|            | Unsolicited Response Format                         |     |

| Figure 8.  | Command Ring Buffer (CORB)                          | .63 |

| Figure 9.  | CORB Initialization                                 | .64 |

| Figure 10. | Transmitting Commands via the CORB                  | .65 |

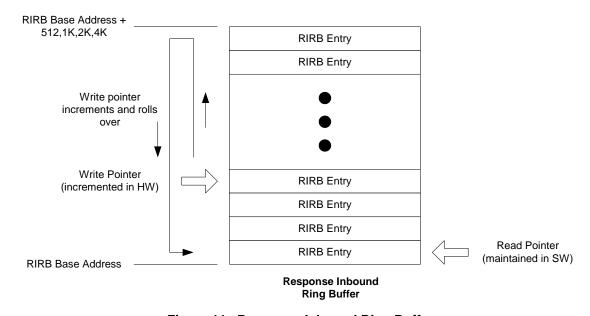

|            | Response Inbound Ring Buffer                        |     |

|            | Initializing the RIRB                               |     |

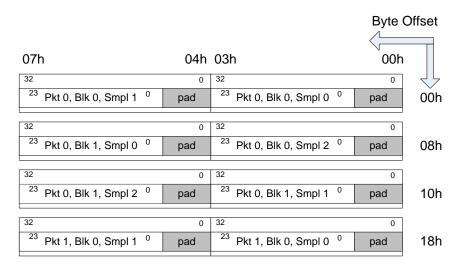

| Figure 13. | A 24-bit, Three-Channel, 96-kHz Stream in Memory    | .70 |

| Figure 14. | High Definition Audio Link Conceptual View          | .77 |

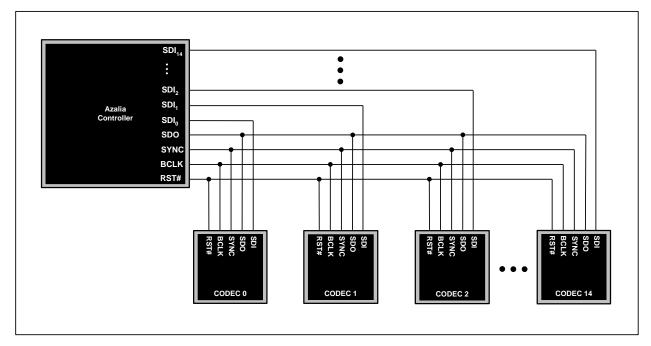

| Figure 15. | Basic High Definition Audio System                  | .79 |

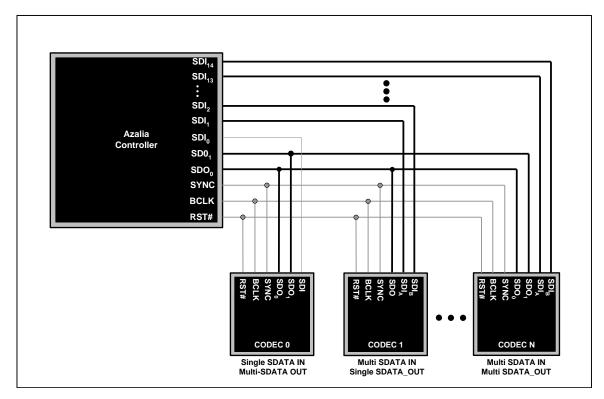

|            | Serial Data Bandwidth Scaling                       |     |

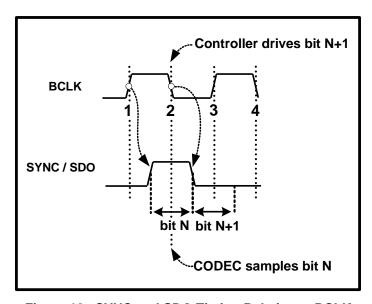

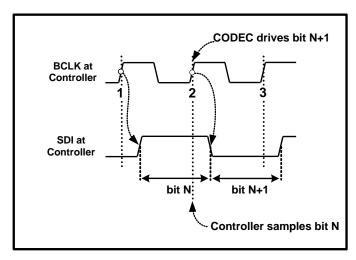

| Figure 17. | SDO and SDI Bit Timing                              | .81 |

|            | SYNC and SDO Timing Relative to BCLK                |     |

|            | SDI Timing Relative to BCLK                         |     |

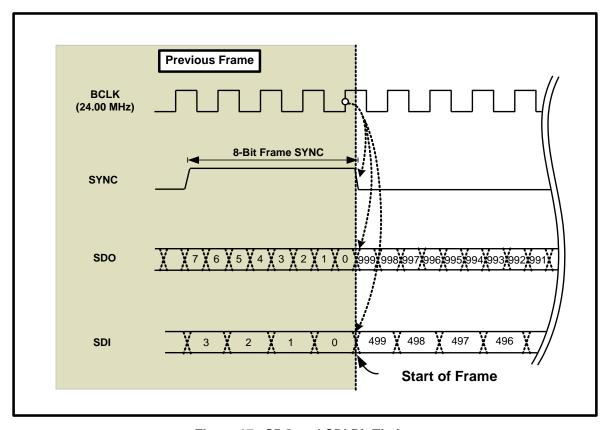

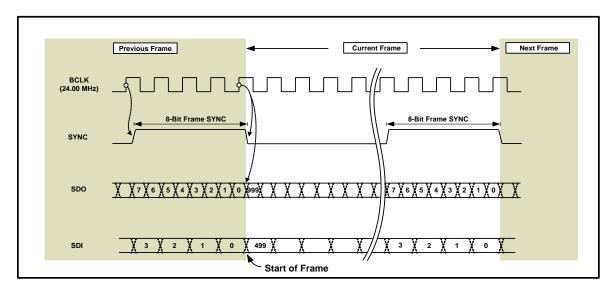

|            | Frames Demarcation                                  |     |

| Figure 21. | Frame Composition                                   | .84 |

| Figure 22. | Outbound Stream Tag Format and Transmission         | .86 |

|            | Outbound Frame With Null Field                      |     |

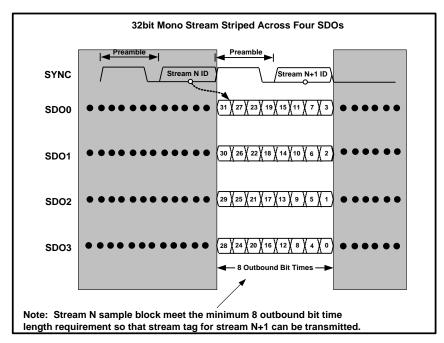

|            | Outbound Striping Example                           |     |

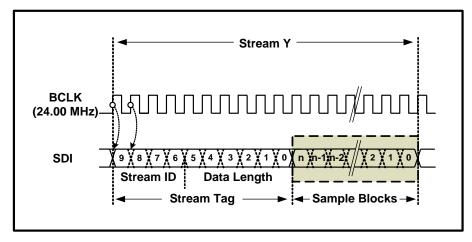

|            | Inbound Tag Format and Transmission                 |     |

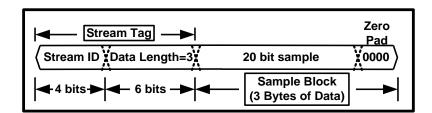

|            | 20-bit Mono Stream With Data Padded to Nearest Byte |     |

|            | Inbound Frame With No Null Field                    |     |

| •          | Link Reset Entry Sequence                           |     |

| •          | Link Reset Exit Sequence                            |     |

|            | Codec Initialization Sequence                       |     |

|            | Codec Connect and Turnaround Frames                 |     |

|            | Codec Address Assignment Frame                      |     |

| •          | Resume From External Event                          |     |

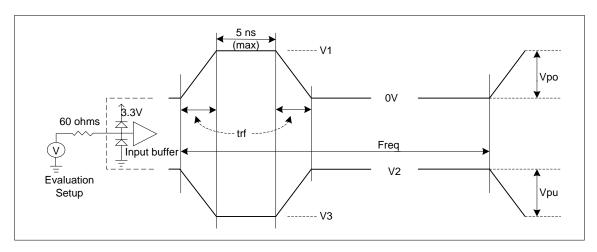

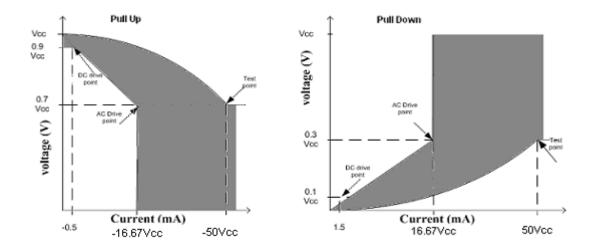

|            | V/I Curves for SDO Buffers                          |     |

|            | V/I Curves for SDI Buffers                          |     |

|            | Maximum AC Waveforms for 3.3V Signaling             |     |

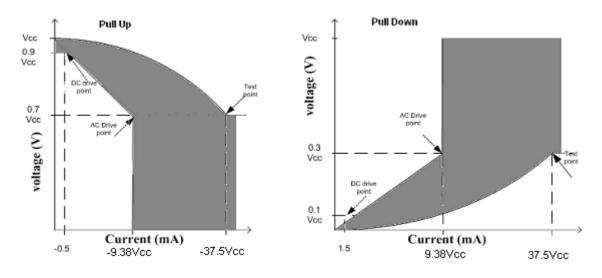

|            | V/I Curves for SDO Buffers                          |     |

|            | V/I Curves for SDI Buffers                          |     |

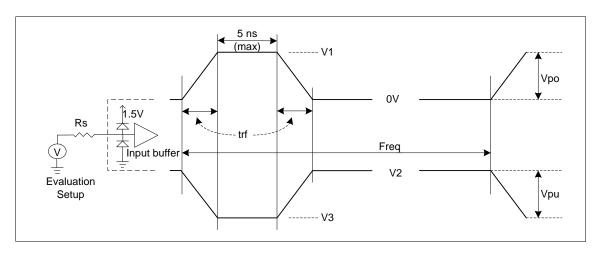

|            | Maximum AC Waveforms for 1.5V Signaling             |     |

|            | Slew Rate and Minimum Valid Delay                   |     |

|            | Maximum Valid Delay                                 |     |

|            | Timing Parameters as Measured at the Controller     |     |

| •          | Timing Parameters as Measured at the Codec          |     |

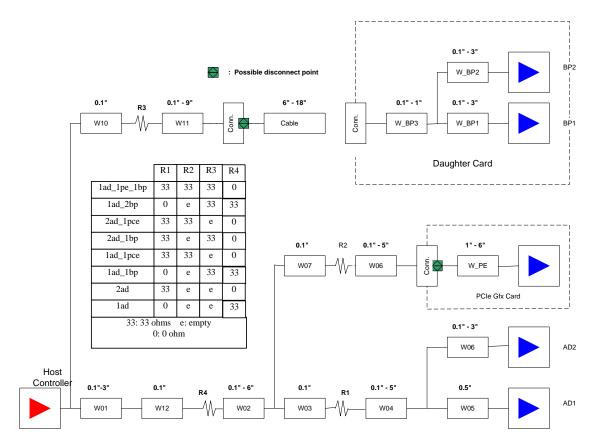

|            | Desktop Platform Configurations                     |     |

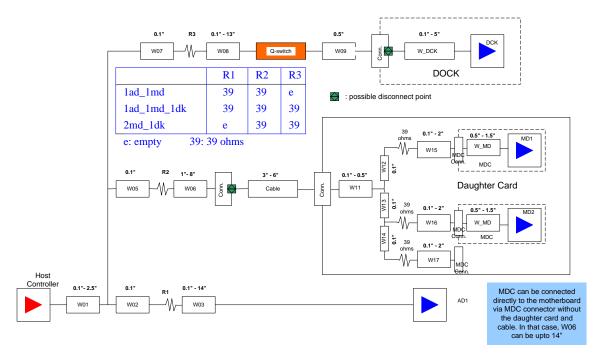

|            | Mobile Star Platform Configurations                 |     |

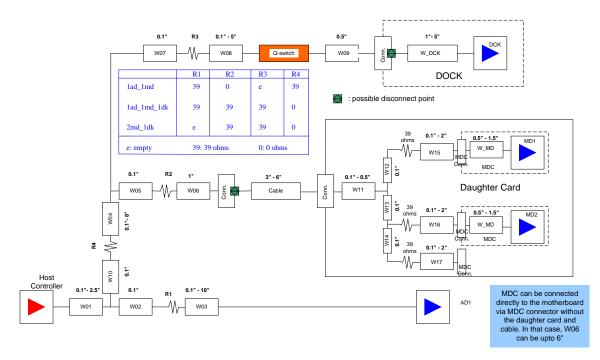

|            | Branched Mobile Configuration                       |     |

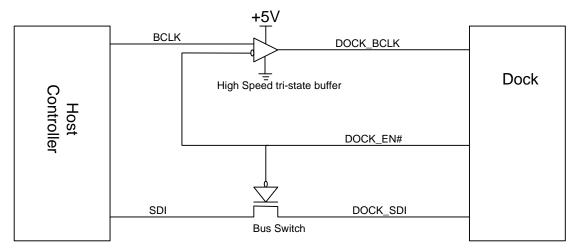

| rigure 47. | Hot Attach, Asynchronous Solution                   | 123 |

| Figure 48.  | Hot Attach, Synchronous Solution                                               | 124               |

|-------------|--------------------------------------------------------------------------------|-------------------|

| Figure 49.  | Module-Based Codec Architecture                                                | 128               |

| Figure 50.  | Codec Module Addressing Scheme                                                 | 129               |

|             | Connection Lists                                                               |                   |

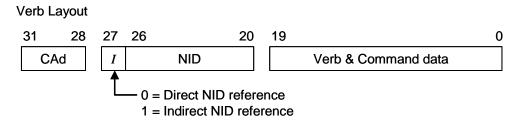

| Figure 52.  | Verb Addressing Fields                                                         | 131               |

| Figure 53.  | Audio Output Converter Widget                                                  | 135               |

| Figure 54.  | Audio In Converter Widget                                                      | 135               |

| Figure 55.  | Pin Widget                                                                     | 136               |

| Figure 56.  | Mixer Widget                                                                   | 137               |

| Figure 57.  | Selector Widget                                                                | 138               |

|             | Command Field Format                                                           |                   |

|             | Response Field Format                                                          |                   |

|             | Get Connection List Entry (Short Form) Response Format                         |                   |

| Figure 61.  | Get Connection List Entry (Long Form) Response Format                          | 143               |

|             | Amplifier Gain/Mute Get Payload                                                |                   |

|             | Amplifier Gain/Mute Get Response                                               |                   |

|             | Amplifier Gain/Mute Set Payload                                                |                   |

|             | S/PDIF IEC Control (SIC) Bits                                                  |                   |

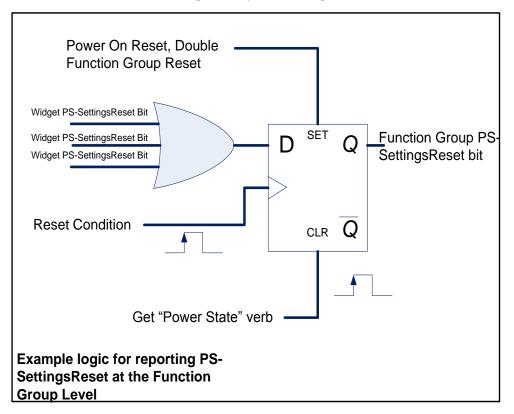

|             | Example of Function Group SettingsReset logic                                  |                   |

|             | PinCntl Format                                                                 |                   |

|             | EnableUnsol Format                                                             |                   |

|             | Intrinsic Unsolicited Response Format                                          |                   |

|             | Generic Non-Intrinsic Unsolicited Response Format                              |                   |

|             | Content Protection Non-Intrinsic Unsolicited Response Format                   |                   |

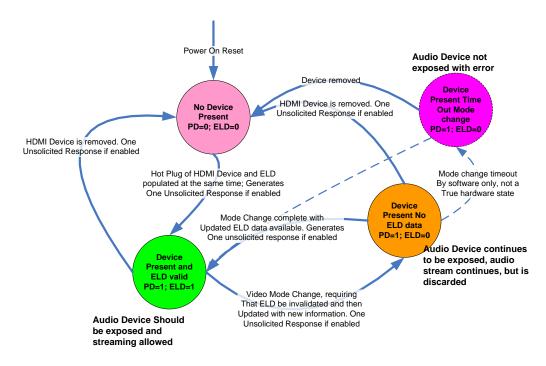

| Figure 72.  | PD and ELDV unsolicited responses flow for digital display codecs              | 166               |

|             | Implementation Identification Value                                            |                   |

|             | Configuration Data Structure                                                   |                   |

|             | Stripe Control Register                                                        |                   |

| •           | ELD Data Response Format                                                       |                   |

|             | ELD Memory Structure                                                           |                   |

|             | Header Block of ELD Memory Structure                                           |                   |

|             | Baseline Block of ELD Memory Structure for ELD_Ver = 00010b                    |                   |

|             | Audio HDCP Request Diagram                                                     |                   |

|             | Vendor ID Response Format                                                      |                   |

| •           | Revision ID Response Format                                                    |                   |

|             | Subordinate Node Count Response Format                                         |                   |

|             | Function Group Type Response Format                                            |                   |

|             | Audio Function Group Capabilities Response Format                              |                   |

|             | Audio Widget Capabilities Response Format                                      |                   |

|             | Supported PCM Size, Rates Return Format                                        |                   |

|             | Supported Stream Formats Response Format  Pin Capabilities Response Format     |                   |

| •           | ·                                                                              |                   |

|             | VRef Bit Field Amplifier Capabilities Response Format                          |                   |

|             |                                                                                |                   |

|             | Connection List Length Response Format  Supported Power States Response Format |                   |

|             | Processing Capabilities Response Format                                        |                   |

|             | GP I/O Capabilities Response Format                                            |                   |

|             | Volume Knob Capabilities Response Format                                       |                   |

| i iguit 30. | volume isnob capabilities isesponse i dilliat                                  | ∠ I <del>'4</del> |

| Figure 97. | Jack Detect Circuit                                   | 220 |

|------------|-------------------------------------------------------|-----|

| Figure 98. | De-bounce and UR timing (link clock is running)       | 221 |

| •          | De-bounce and wake timing (link clock is not running) |     |

| •          | Test Modes                                            |     |

| Tables                 |                                                           |    |

|------------------------|-----------------------------------------------------------|----|

| Table 1.               | Register Type Definitions                                 | 24 |

| Table 2.               | Controller Registers Summary                              | 25 |

| Table 3.               | Global Capabilities                                       | 28 |

| Table 4.               | Minor Version                                             | 29 |

| Table 5.               | Major Version                                             | 29 |

| Table 6.               | Output Payload Capability                                 |    |

| Table 7.               | Input Payload Capability                                  |    |

| Table 8.               | Global Control Register                                   |    |

| Table 9.               | Wake Enable                                               |    |

| Table 10.              | Wake Status                                               |    |

| Table 11.              | Global Status                                             |    |

| Table 12.              | Output Payload Capability                                 |    |

| Table 13.              | Input Payload Capability                                  |    |

| Table 14.              | Interrupt Control Register                                |    |

| Table 15.              | Interrupt Status Register                                 |    |

| Table 16.              | Wall Clock Counter                                        |    |

| Table 17.              | Stream Synchronization                                    |    |

| Table 18.              | CORB Lower Base Address                                   |    |

| Table 19.              | CORB Upper Base Address                                   |    |

| Table 20.              | CORB Write Pointer                                        |    |

| Table 21.              | CORB Read Pointer                                         |    |

| Table 22.              | CORB Control                                              |    |

| Table 23.              | CORB Status                                               |    |

| Table 24.              | CORB Size                                                 |    |

| Table 25.              | RIRB Lower Base Address                                   |    |

| Table 26.              | RIRB Upper Base Address                                   |    |

| Table 27.              | RIRB Write Pointer                                        |    |

| Table 28.              | RIRB Response Interrupt Count                             | Δ( |

| Table 29.              | RIRB Control                                              |    |

| Table 30.              | RIRB Status                                               |    |

| Table 31.              | RIRB Size                                                 |    |

| Table 31.              | DMA Position Lower Base Address                           |    |

| Table 33.              | DMA Position Upper Base Address                           |    |

| Table 33.              | Stream Descriptor <i>n</i> Control                        |    |

| Table 34.              | Stream Descriptor <i>n</i> Status                         |    |

| Table 36.              | Stream Descriptor <i>n</i> Link Position in Buffer        |    |

| Table 37.              | Stream Descriptor <i>n</i> Cyclic Buffer Length           |    |

| Table 37.              | Stream Descriptor <i>n</i> Last Valid Index               |    |

| Table 38.              | Stream Descriptor <i>n</i> FIFO Size                      |    |

| Table 40.              | Stream Descriptor <i>n</i> Format                         |    |

| Table 41.              | Stream Descriptor <i>n</i> Lower Base Address             |    |

| Table 41.              | Stream Descriptor <i>n</i> Upper Base Address             |    |

| Table 42.              | Wall Clock Counter                                        |    |

| Table 43.              | Link Position in Buffer <i>n</i> Alias                    |    |

| Table 44.<br>Table 45. | Immediate Command Output Interface                        |    |

| Table 45.              | Immediate Command Input Interface                         |    |

| Table 46.<br>Table 47. | Immediate Command Input InterfaceImmediate Command Status |    |

| 1 abit 41.             | mmediale Command Status                                   |    |

| Table 48. | DMA Position in Current Buffer                    | 55  |

|-----------|---------------------------------------------------|-----|

| Table 49. | Buffer Descriptor                                 | 55  |

| Table 50. | Buffer Descriptor                                 |     |

| Table 51. | Command Output Ring Buffer                        | 56  |

| Table 52. | Response Input Ring Buffer                        |     |

| Table 53. | PCM Format Structure                              | 58  |

| Table 54. | RIRB Entry Format                                 | 68  |

| Table 55. | High Definition Audio Link Signal Descriptions    | 78  |

| Table 56. | Defined Sample Rates                              | 92  |

| Table 57. | Sample Transmission Rate                          | 93  |

| Table 58. | 3.3V DC Specification                             | 105 |

| Table 59. | SDO Buffer AC Specification                       | 108 |

| Table 60. | SDI Buffer AC Specification                       | 108 |

| Table 61. | Parameters for Maximum AC Signaling Waveforms     | 109 |

| Table 62. | 1.5V DC Specification                             |     |

| Table 63. | SDO Buffer AC Specification                       |     |

| Table 64. | SDI Buffer AC Specification                       | 113 |

| Table 65. | Parameters for Maximum AC Signaling Waveforms     | 114 |

| Table 66. | Resistance Value for the AC Rating Waveform       |     |

| Table 67. | Measurement Condition Parameters                  | 115 |

| Table 68. | Timing Parameters at the Controller               | 116 |

| Table 69. | Timing Parameters at the Codec                    | 117 |

| Table 70. | Total Trace Mismatch                              |     |

| Table 71. | Maximum Trace Lengths                             | 119 |

| Table 72. | Get Parameter Command                             | 141 |

| Table 73. | Connection Select Control                         | 142 |

| Table 74. | Connection List Entry Control                     |     |

| Table 75. | Processing State                                  |     |

| Table 76. | Coefficient Index                                 |     |

| Table 77. | Processing Coefficient                            | 145 |

| Table 78. | Amplifier Gain/Mute                               | 145 |

| Table 79. | Converter Format                                  | 147 |

| Table 80. | SPDIF Sync Preamble Bits                          |     |

| Table 81. | S/PDIF Converter Control 1, 2, 3 and 4            |     |

| Table 82. | Power State                                       | 151 |

| Table 83. | Power State Field Definition                      |     |

| Table 84. | Persisted Settings across Resets and power states |     |

| Table 85. | Converter Control                                 |     |

| Table 86. | SDI Select                                        |     |

| Table 87. | Enable VRef                                       |     |

| Table 88. | VRefEn Values                                     |     |

| Table 89. | EPT Values                                        |     |

| Table 90. | Connection Select Control                         |     |

| Table 91. | Intrinsic Unsolicited Response Fields             |     |

| Table 92. | Pin Sense                                         |     |

| Table 93. | EAPD/BTL Enable                                   |     |

| Table 94. | GPI Data                                          |     |

| Table 95. | GPI Wake Mask                                     |     |

| Table 96. | GPI Unsolicited Enable                            | 170 |

| Table 97.  | GPI Sticky Mask                    |     |

|------------|------------------------------------|-----|

| Table 98.  | GPO Data                           | 171 |

| Table 99.  | GPIO Data                          | 171 |

| Table 100. | GPIO Enable                        | 172 |

| Table 101. | GPIO Direction                     | 172 |

| Table 102. | GPIO Wake Enable                   | 173 |

| Table 103. | GPIO Unsolicited Enable            | 173 |

| Table 104. | GPIO Sticky Mask                   | 174 |

| Table 105. | Beep Generation                    | 174 |

| Table 106. | Volume Knob Control                | 175 |

| Table 107. | Implementation Identification      | 177 |

| Table 108. | Configuration Default              | 178 |

| Table 109. | Port Connectivity                  | 179 |

| Table 110. | Location                           | 180 |

| Table 111. | Default Device                     | 180 |

| Table 112. | Connection Type                    | 181 |

| Table 113. | Color                              | 181 |

| Table 114. | Misc                               | 181 |

| Table 116. | Function Reset                     | 183 |

| Table 117. | ELD Data                           | 184 |

| Table 118. | ELD_Ver Encoding                   | 186 |

| Table 119. | MNL Encoding                       | 187 |

| Table 120. | CEA_EDID_Ver Encoding              | 187 |

| Table 121. | Conn_Type Encoding                 | 187 |

| Table 122. | SAD_Count Encoding                 | 188 |

| Table 123. | Aud_Synch_Delay Encoding           | 188 |

| Table 124. | Converter Channel Count            | 189 |

| Table 125. | DIP-Size                           | 190 |

| Table 126. | DIP-Size Packet Index              | 190 |

| Table 127. | DIP-Index                          | 191 |

| Table 128. | DIP-Index Packet Index             | 192 |

| Table 129. | DIP-Data                           | 192 |

| Table 130. | DIP-XmitCtrl                       | 193 |

| Table 131. | DIP-XmitCtrl Value                 | 193 |

| Table 132. | Protection Control                 | 194 |

| Table 133. | Current Encryption State (CES)     | 194 |

| Table 134. | Ready Indication                   |     |

| Table 135. | Content Protection (CP) State      |     |

| Table 136. | ASP Channel Mapping                |     |

| Table 137. | Node Type                          |     |

| Table 138. | Widget Type                        |     |

| Table 139. | Bit Depth and Sample Rate          |     |

| Table 140. | Required Support for Parameters    |     |

| Table 141. | Required Support for Verbs         |     |

| Table 142. | High Definition Audio Codec Pinout |     |

| Table 143  | lack Detect Resistor Assignments   |     |

# 1 Introduction

# 1.1 Scope and Layout of This Document

This document is divided into seven chapters.

Chapter 1 is an introduction to the specification. It contains a high level overview of the specification layout, goals, and non-goals.

Chapter 2 provides an introduction to the High Definition Audio architecture.

Chapter 3 describes the details of a High Definition Audio controller register set, as well as the data structures used in programming the controller. Software programmers and controller hardware designers will find this chapter of interest.

Chapter 4 is a software programming reference designed to aid in the development of High Definition Audio compliant software, including controller and codec programming. This chapter is of primary interest to those writing High Definition Audio compliant software or to readers looking for more detail about the functionality of the hardware.

Chapter 5 describes the High Definition Audio physical link protocol. Designers of controller and codec hardware will find this chapter of interest.

Chapter 6 describes the physical link electrical requirements necessary for interfacing High Definition Audio controllers with codecs on the link. Designers of controller and codec hardware will find this chapter of interest.

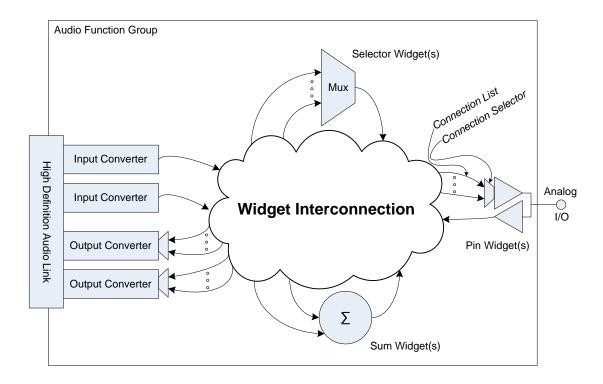

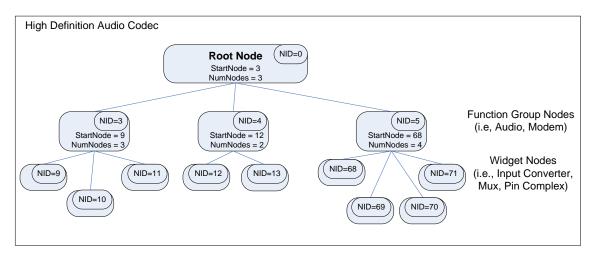

Chapter 7 describes the High Definition Audio codec architecture. Information on codec architectural building blocks, as well as the software programming model, is provided. Codec hardware designers and software programmers will find this chapter of interest.

### 1.2 Motivation and Goals

The primary goals of the High Definition Audio (HD Audio) specification are to describe an infrastructure to support high quality audio in a PC environment. The specification includes the definition of the controller register set, the physical link description, the codec programming model, and codec architectural components.

The High Definition Audio specification primarily focuses on audio functionality for purposes of architectural description. Other codec types are implementable within the High Definition Audio architecture. In particular, voice band modems codecs (v.92, for instance) are supported, as the modem data rates and types of data are typically a subset of the audio data rates and types. See Section 7.2.2.2 for more information about modem support. In general, the High Definition Audio specification does not prohibit the implementation of other codec types provided that they comply with all codec requirements laid out in Chapters 3 through 7 of this specification.

#### 1.2.1 AC'97 Compatibility

The High Definition Audio architecture was not developed with the intent of being backward compatible with AC'97. Unlike AC' 97, the primary goal of the High Definition Audio Architecture is to develop a uniform programming interface and to provide fundamental flexibility and capabilities beyond those supported by AC'97. Therefore, the High Definition Audio architecture and specification must be considered entirely a separate specification from AC'97, implying no backward compatibility. Specifically, link protocol and operation between these two specifications is not compatible. AC'97 and High Definition Audio codecs cannot be mixed on the same link or behind the same controller.

#### 1.2.2 Feature List

Support for 15 input and 15 output streams at a time

Extensive support for scalability in controller, link, and codec design to optimize for cost, performance, or features

Sample rate support ranging from 6 kHz to 192 kHz.

Support for 8-, 16-, 20-, 24-, and 32-bit sample resolution per stream.

Up to 16 channels per stream.

48-Mbps outbound link transfer rate per **SDO**.

24-Mbps inbound transfer rate per SDI.

Support for striping on optional higher order **SDO** link pins to double or quadruple available outbound bandwidth.

Support for multi-**SDI** codecs to increase available inbound link bandwidth.

Codec architecture is fully discoverable, allowing for codec design flexibility.

Audio codecs, modem codecs, and vendor defined codecs are all supported.

Command/Response codec communication mechanism for extensibility and flexibility.

Support for system wake generation from all codecs types.

Support for codec interrupt generation through Unsolicited Responses.

Extensive, fine grained power management control in the codec.

Industry standard 48-pin QFP package and pinout for codec.

Audio codecs support advanced jack detection and jack sensing for device discoverability and jack retasking.

#### 1.2.3 Related Documents

PCI Local Bus Specification, Rev. 2.3

PCI Power Management Interface Specification, Rev. 1.2

PCI Express\* Base Specification, Rev. 1.0a

Advanced Configuration and Power Interface Specification, Rev. 2.0

# 2 Architecture Overview

The purpose of this chapter is to introduce terminology specific to the High Definition Audio architecture, which will be used throughout this specification, and to provide a qualitative introduction to or theory of operation for the High Definition Audio architecture. This conceptual overview should give the reader a foundation for ease of navigating through the interface and syntactical details delivered in the balance of the specification. It is not the intent of this chapter to provide any syntactic, timing, or otherwise quantitative definitions.

# 2.1 Hardware System Overview

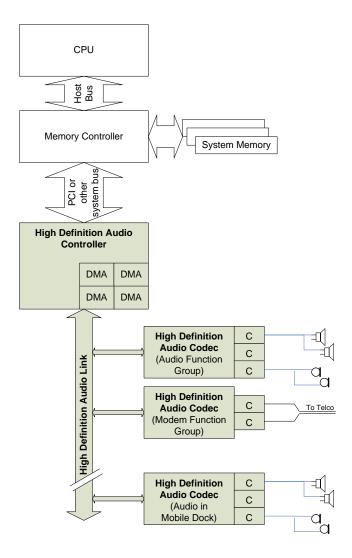

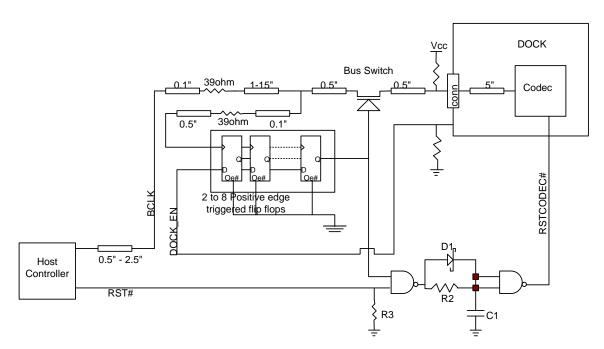

The hardware building blocks of the High Definition Audio architecture are shown in Figure 1.

Figure 1. High Definition Audio Architecture Block Diagram

**Controller:** The High Definition Audio controller is a bus mastering I/O peripheral, which is attached to system memory via PCI or other typical PC peripheral attachment host interface. It contains one or more DMA engines, each of which can be set up to transfer a single audio "stream" to memory from the codec or from memory to the codec depending on the DMA type. The controller implements all the memory mapped registers that comprise the programming interface as defined in Section 3.3.

**Link:** The controller is physically connected to one or more codecs via the High Definition Audio Link. The link conveys serialized data between the controller and the codecs. It is optimized in both bandwidth and protocol to provide a highly cost effective attach point for low cost codecs. The link also distributes the sample rate time base, in the form of a link *bit clock* (**BCLK**), which is generated by the controller and used by all Codecs. The link protocol supports a variety of sample rates and sizes under a fixed data transfer rate.

**Codec:** One or more codecs connect to the link. A codec extracts one or more audio streams from the time multiplexed link protocol and converts them to an output stream through one or more converters (marked "C"). A converter typically converts a digital stream into an analog signal (or vise versa), but may also provide additional support functions of a modem and attach to a phone line, or it may simply de-multiplex a stream from the link and deliver it as a single (un-multiplexed) digital stream, as in the case of S/PDIF. The number and type of converters in a codec, as well as the type of jacks or connectors it supports, depend on the codec's intended function. The codec derives its sample rate clock from a clock broadcast (**BCLK**) on the link. High Definition Audio Codecs are operated on a standardized command and control protocol as defined in Section 4.4.

**Acoustic Device:** These devices include speakers, headsets, and microphones, and the specifications for them are outside the scope of this specification, except for discovery capabilities such as defined in Section 7.3.3.15.

**Packaging Alternatives:** Figure 1 suggests that codecs can be packaged in a variety of ways, including integration with the controller, permanent attachment on the motherboard, modular ("add-in") attachment, or included in a separate subsystem such as a mobile docking station. In general the electrical extensibility and robustness of the link is the limiting factor in packaging options. This specification does not define or standardize packaging options beyond the standardized footprint of a codec as defined in Section 7.4.1 of this specification.

#### 2.2 Streams and Channels

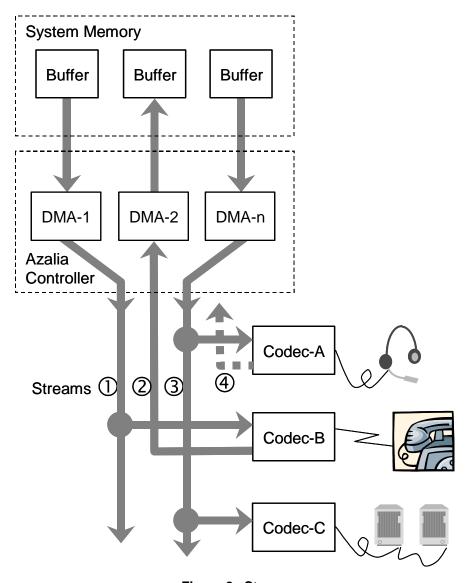

The High Definition Audio architecture introduces the notion of streams and channels for organizing data that is to be transmitted across the High Definition Audio link. A *stream* is a logical or virtual connection created between a system memory buffer(s) and the codec(s) rendering that data, which is driven by a single DMA channel through the link. A stream contains one or more related components or *channels* of data, each of which is dynamically bound to a single converter in a codec for rendering. For example, a simple stereo stream would contain two channels; left and right. Each sample point in that stream would contain two samples: L and R. The samples are packed together as they are represented in the memory buffer or transferred over the link, but each are bound to a separate D-to-A converter in the codec.

Figure 2 illustrates several important concepts. First, a stream is either output or input. Output streams are broadcast and may be bound to more than one codec; e.g., stream #3 might be a two-channel (stereo) stream rendered by both Codec-A on a headset and by Codec-C on speakers. Input streams may be bound to only a single codec; e.g., stream #2 contains the single channel – the input side of a modem.

Each active stream must be connected through a DMA engine in the controller. If a DMA engine is not available, a stream must remain inactive until one becomes available; e.g., stream #4 in this example (presumably the one bound to the headset microphone) is not connected to a DMA engine and is therefore inactive.

As a general rule, all channels within a stream must have the same sample rate and same sample size.

Figure 2. Streams

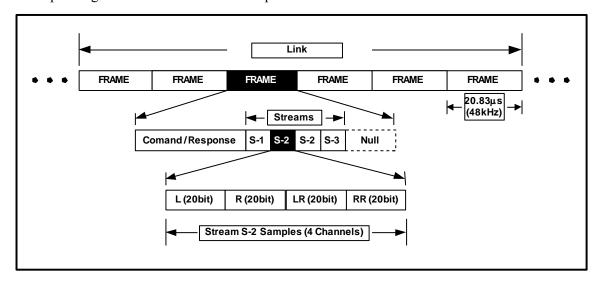

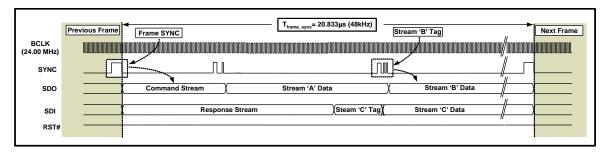

Figure 3 shows how streams and channels are transferred on the link. Each input or output signal in the link transmits a series of packets or *frames*. A new frame starts exactly every 20.83  $\mu$ s, corresponding to the common 48-kHz sample rate.

Figure 3. Conceptual Frame Composition

The first breakout shows that each frame contains command or control information and then as many stream sample blocks (labeled S-1, S-2, S-3) as are needed. The total number of streams supportable is limited by the aggregate content of the streams; any unused space in the frame is filled will nulls. Since frames occur at a fixed rate, if a given stream has a sample rate that is higher or lower than 48 kHz, there will be more or less than one sample block in each frame for that stream. Some frames may contain two sample blocks (e.g., S-2 in this illustration) and some may contain none. Section 5.4.1 describes in detail the methods of dealing with sample rates other than 48 kHz.

The second breakout shows that a single stream 2 (S-2) sample block is composed of one sample for each channel in that stream. In this illustration, stream 2 (S-2) has four channels (L, R, LR, RR) and each channel has a 20-bit sample; therefore, the stream sample block uses 80 bits. Note that stream 2 (S-2) is a 96 kHz stream since two sample blocks are transmitted per 20.83  $\mu$ s (48 kHz) frame.

# 2.3 DMA Channel Operation

In the High Definition Audio architecture, all audio or modem data is transferred to or from the codecs by the DMA engines in the High Definition Audio controller, which provide standard scatter/gather DMA channel operation. The DMA engines must account for the behavior of their memory attachment port, especially latency, and pre-fetch and buffer enough data on each stream (one or two frames) to ensure there will not be an underrun or overrun on the isochronous High Definition Audio link.

Each DMA engine, when it is enabled, walks through a memory-based list of buffer descriptors, each of which identifies an arbitrary length data buffer. It processes each buffer in turn transferring data to or from the codec. The controller's register space for each DMA engine includes a pointer

to the head of the buffer descriptor list, as well as a register identifying the last valid pointer in the list, as is described in Section 3.1.

#### 2.4 Initialization and Enumeration

Enumeration takes place at three distinct levels in the High Definition Audio architecture.

**Controller:** The High Definition Audio controller is initialized and enumerated using the standard PCI enumeration mechanisms, or as is appropriate to the system interface. Other than defining memory-mapped register space, that process is outside the scope of this specification.

**Codec:** After link reset, and during initialization, the link protocol provides each codec on the link a unique ID. This process is described in Section 5.5.3 After the controller has been initialized and the software driver loaded, the software queries each ID on the link to determine the capabilities of the corresponding codec. Hot plugging of codecs is supported for docking solution.

**Peripheral Devices:** When the codec capabilities are enumerated, the types of input/output jacks can be determined through the codec command and control mechanisms under control of the driver. In addition, codec will be able to detect whether a peripheral device is plugged into the jack, and, in some cases, may be able to determine the class of device involved.

# 3 Register Interface

This chapter outlines the High Definition Audio Controller register interface. All High Definition Audio controllers must implement the registers defined in Section 3.3. The registers defined in Section 3.4 are optional and are not required by this specification.

# 3.1 Introduction to Controller Registers

# 3.1.1 Terminology

Table 1 lists terminology used in the definition of registers in this specification.

Table 1. Register Type Definitions

| Register<br>Attribute | Meaning                                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| RO                    | Read only register                                                                                                                 |

| RW                    | Read-Write                                                                                                                         |

| RW1C                  | Read-only status, write-1-to-clear status register                                                                                 |

| ROS                   | Sticky bit–Read-only register                                                                                                      |

| RWS                   | Sticky bit–Read-Write register                                                                                                     |

| RW1CS                 | Sticky bit-Read-only status, Write-1-to-clear status register.                                                                     |

| HWINIT                | Hardware initialized; bits are read-only and cannot be reset.                                                                      |

| RsvdP                 | Reserved; software must do a read-modify-write to preserve the value of bits.                                                      |

| RsvdZ                 | Reserved; software must use 0's for writes to bits.                                                                                |

| RSM                   | Bit(s) are in the "Resume Well"; i.e., they maintain their state in any power state from which the controller may wake the system. |

# 3.1.2 General Register Behaviors and Access Requirements

All controller registers must be addressable as byte, Word, and Dword quantities. The software must always make register accesses on natural boundaries; Dword accesses must be on Dword boundaries; Word accesses must be on Word boundaries; etc.

Software must also properly handle reserved bits. Reserved bits may be designated "RsvdP" or "RsvdZ." Bits marked "RsvdP" must be preserved using read-modify-writes, while "RsvdZ" bits must be written as 0's. This handling helps to ensure future compatibility.

Fields or Registers marked as Read Only (RO) when part of a Register that is Read/Write may be written, but the RO bits must contain the exact bit values that are returned when reading the register, e.g. treated as RsvdP. Writing values that do not match values read from a RO field into that RO field may cause indeterminate behavior.

Note that host controllers are not required to support exclusive-access mechanisms (such as PCI LOCK) for accesses to the memory-mapped register space. Therefore, if software attempts

exclusive-access mechanisms to the host controller memory-mapped register space, the results are undefined.

#### 3.1.3 Behavior With 64-bit Addresses

High Definition Audio controllers may have the ability to generate and use 64-bit addresses for system memory. The system software can determine if the controller hardware has this support ability by checking the 64OK bit in the Global Capabilities register. If this bit is a 1, 64-bit addresses can be used.

If the controller does support 64-bit addresses, the system software may use either 64-or 32-bit addresses. All hardware registers which accept a 64 bit address must default the upper 32 bits to 0. If a 32-bit address is then written to the lower 32 bits of the 64-bit register, the address will be correct.

If the controller is capable of generating either 32-or 64-bit addresses, such as a PCI controller, it may be more efficient to generate a 32-bit address if possible, rather than always generating a 64-bit address. In this case, the controller may use a logical "OR" of the upper 32 bits to determine if the address can be correctly represented as a 32-bit address. The specific behavior will depend on the bus on which the High Definition Audio controller resides.

# 3.2 High Definition Audio Controller System Bus Interface Registers